Intel® Xeon® Processor E5-2600 Product Family Uncore Performance Monitoring

62 Reference Number: 327043-001

All MC performance monitor data registers are 48-bit wide. Should a counter overflow (a carry out

from bit 47), the counter will wrap and continue to collect events.

If accessible, software can continuously read the data registers without disabling event collection.

This is a counter that always tracks the number of DRAM clocks (dclks - half of DDR speed) in the iMC.

The dclk never changes frequency (on a given system), and therefore is a good measure of wall clock

(unlike the Uncore clock which can change frequency based on system load). This clock is generally a

bit slower than the uclk (~800MHz to ~1.066GHz) and therefore has less fidelity.

2.5.5 iMC Performance Monitoring Events

2.5.5.1 An Overview:

A sampling of events available for monitoring in the iMC:

• Translated commands: Various Read and Write CAS commands

• Memory commands: CAS, Precharge, Refresh, Preemptions, etc,

• Page hits and page misses.

• Page Closing Events

• Control of power consumption: Thermal Throttling by Rank, Time spent in CKE ON mode,

etc.

and many more.

Internal iMC Queues:

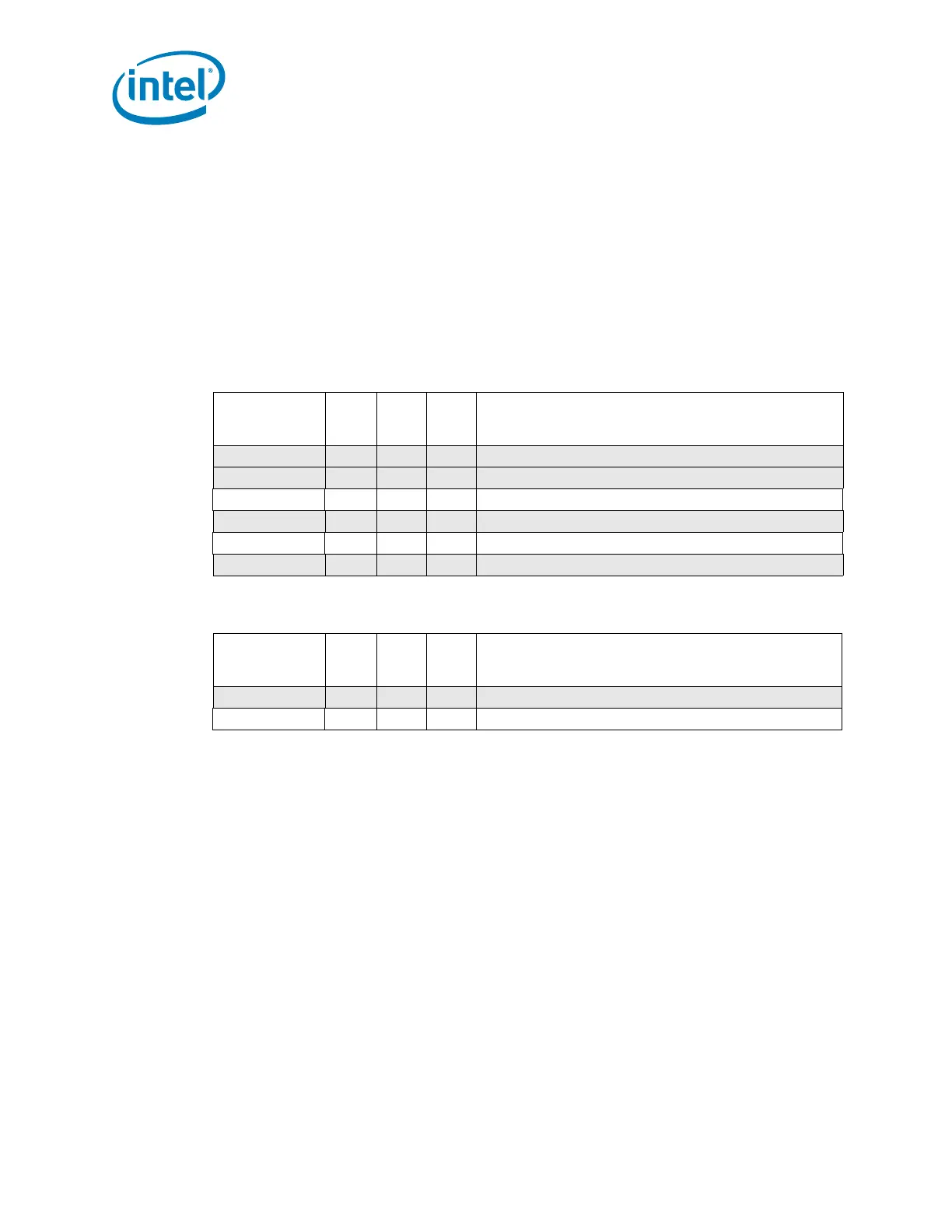

Table 2-62. MC_CHy_PCI_PMON_FIXED_CTL Register – Field Definitions

Field Bits Attr

HW

Reset

Val

Description

rsv 31:24 RV 0 Reserved (?)

rsv 23 RV 0 Reserved. SW must write to 0 else behavior is undefined.

en 22 RW-V 0 Local Counter Enable.

rsv 21:20 RV 0 Reserved. SW must write to 0 else behavior is undefined.

rst 19 WO 0 When set to 1, the corresponding counter will be cleared to 0.

rsv 18:0 RV 0 Reserved (?)

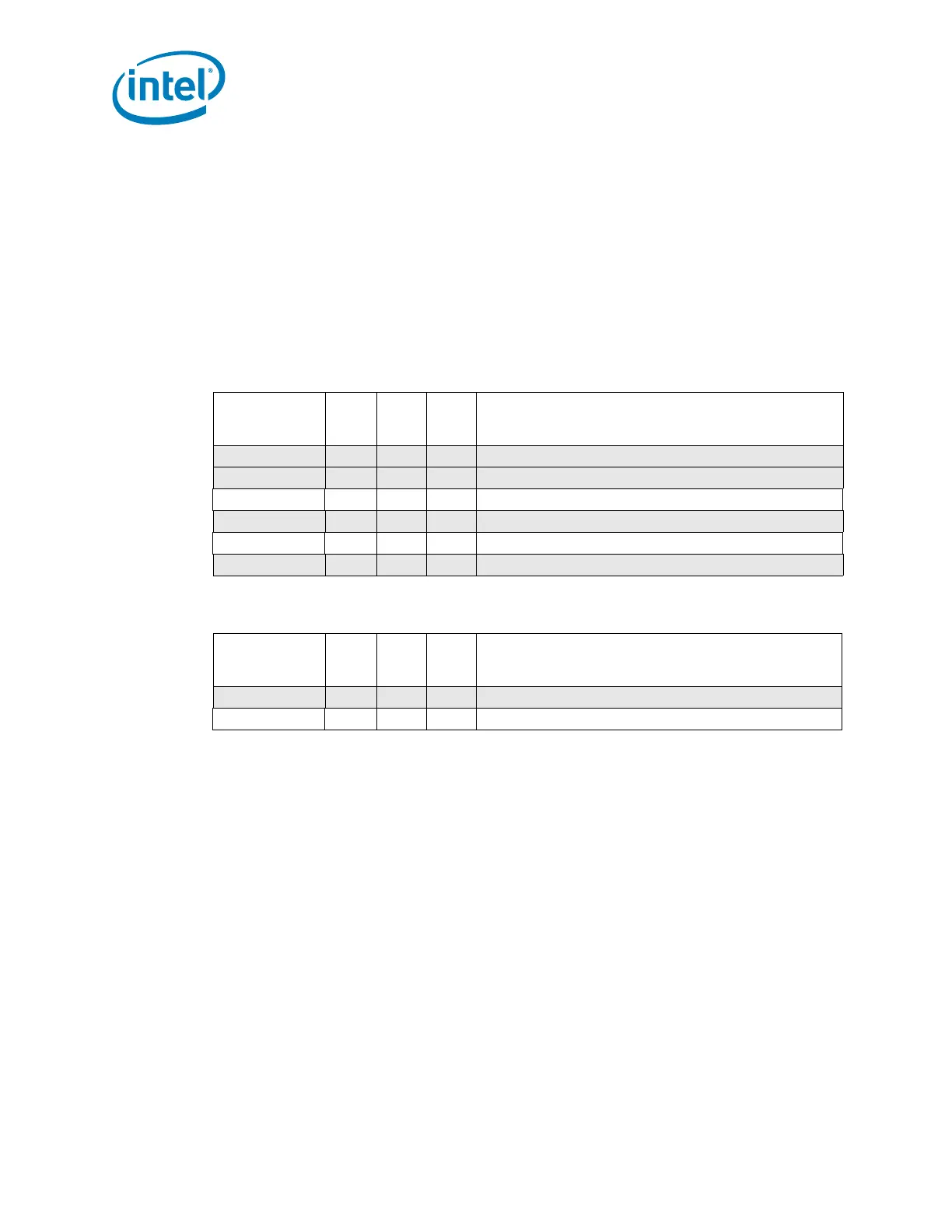

Table 2-63. MC_CHy_PCI_PMON_CTR{FIXED,3-0} Register – Field Definitions

Field Bits Attr

HW

Reset

Val

Description

rsv 63:48 RV 0 Reserved (?)

event_count 47:0 RW-V 0 48-bit performance event counter

Loading...

Loading...