PDP-5071PU

206

1234

1234

C

D

F

A

B

E

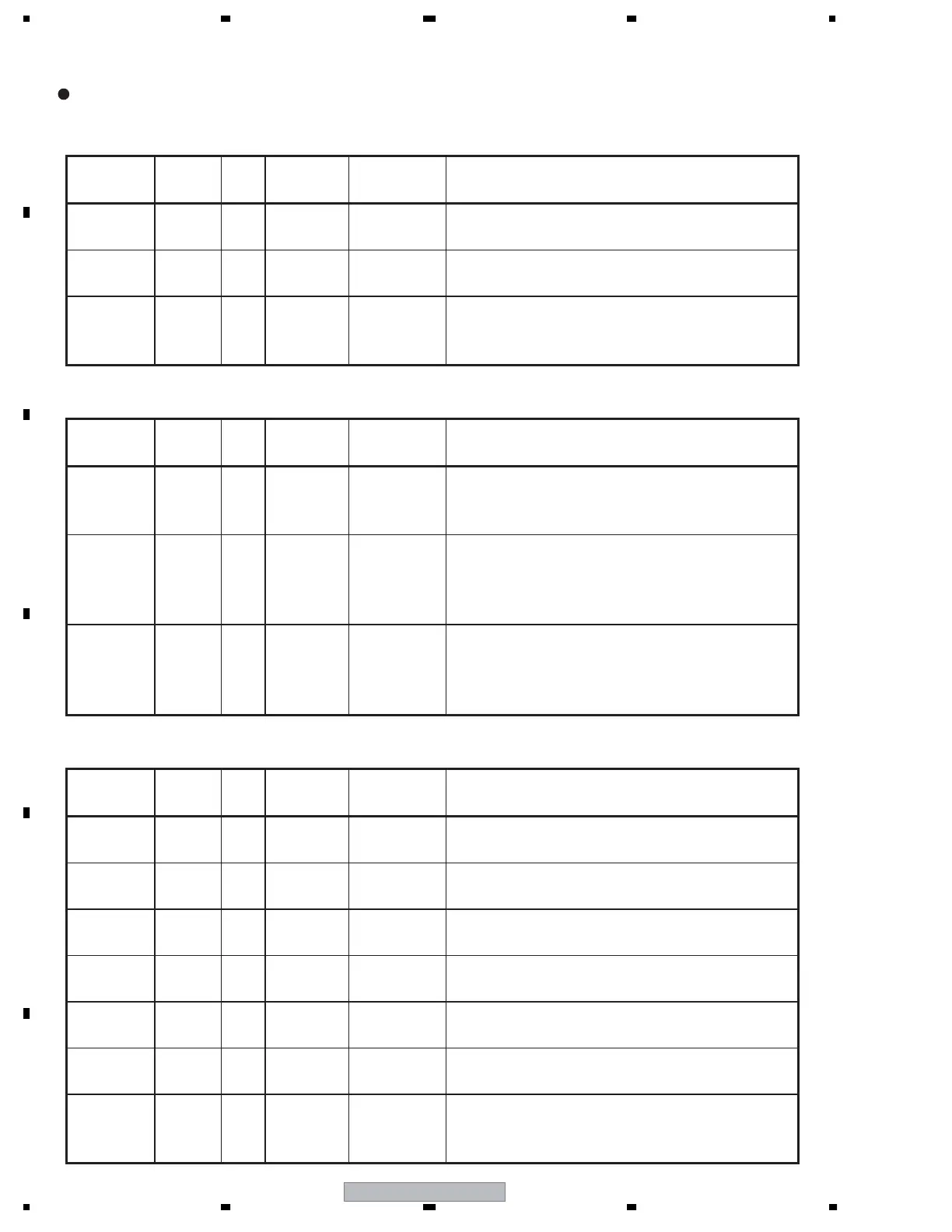

Pin Function

2.5 Clock generator terminal

Acronyms Terminal

number

I/O Level Buffer type

PU/PD [kΩ]

Functions

XI 55 I Analog – Reference clock input

Connect 24.576MHz crystal oscillator.

XO 54 O Analog – Reference clock output

Connect 24.576MHz crystal oscillator.

BCLK8 102 I/O LVTTL

3-state

6 mA Subsequent stage line lock clock monitor input/output

It will become Hi-Z when BCK8OUT (SA1Fh, D5)=0.

Normally, set to BCK8OUT=0 and leave it open.

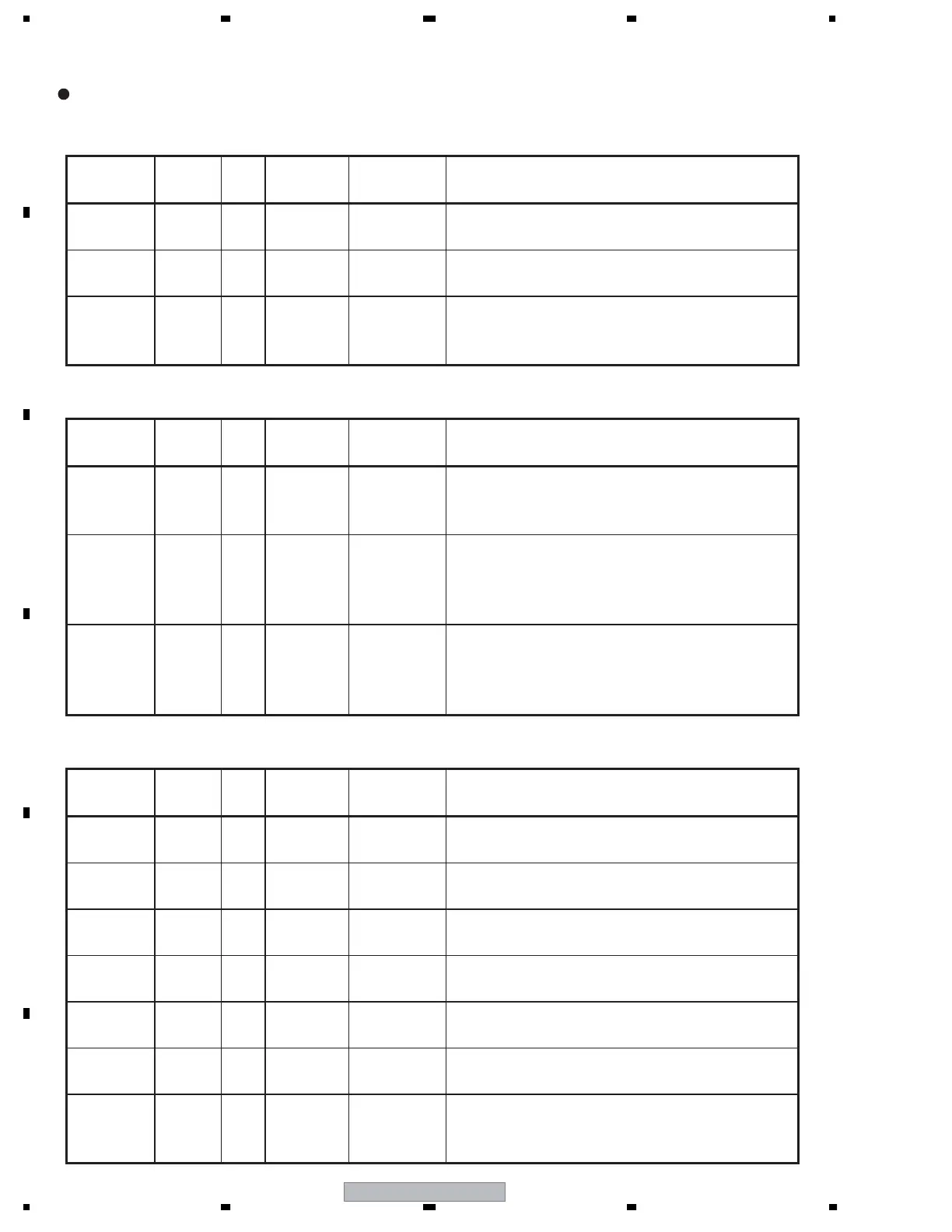

2.6 Terminal for µPD64031A and µPD64032 digital connection

Acronyms Terminal

number

I/O Level Buffer type

PU/PD [kΩ]

Functions

FCLK8 78 I/O LVTTL

3-state

6 mA Front stage burst lock clock input/output

It will become Hi-Z when FCK8S[2:0] (SA21h, D6-D4)=000b.

Normally, set to FCK8S[2:0]=0 and leave it open.

FCKQ 127 I/O LVTTL

3-state

3 mA Sampling clock output for µPD64031A and µPD64032

digital connection.

It will become Hi-Z when FCKQS[2:0] (SA21h, D2-D0)=000b.

Normally, set to FCKQS[2:0]=0 and leave it open.

FOCP 128 I/O LVTTL

3-state

3 mA Clamp pulse output for µPD64031A and µPD64032 digital

connection/timing output (VD) for digital RGB input.

It will become Hi-Z when FOCPS[2:0] (SA23h, D2-D0)=000b.

Normally, set to FOCPS[2:0]=0 and leave it open.

2.7 Terminal for RGB input

Acronyms Terminal

number

I/O Level Buffer type

PU/PD [kΩ]

Functions

DFBI 130 I LVTTL – Fast Blanking signal input for analog RGB input.

DYSI 131 I LVTTL – YS signal input for digital RGB input.

DYMI 134 I LVTTL – YM signal input for digital RGB input.

DCGI 135 I LVTTL – Digital RGB/G signal input

DCBI 136 I LVTTL – Digital RGB/B signal input

DCRI 137 I LVTTL – Digital RGB/R signal input

FCSI 129 I/O LVTTL

3-state

3 mA Sync separation signal input/timing output (HD) for RGB input.

It will become Hi-Z when FCSIS[2:0] (SA22h, D2-D0)=000b.

Normally, set to FCSIS[2:0]=0 and leave it open.

Loading...

Loading...