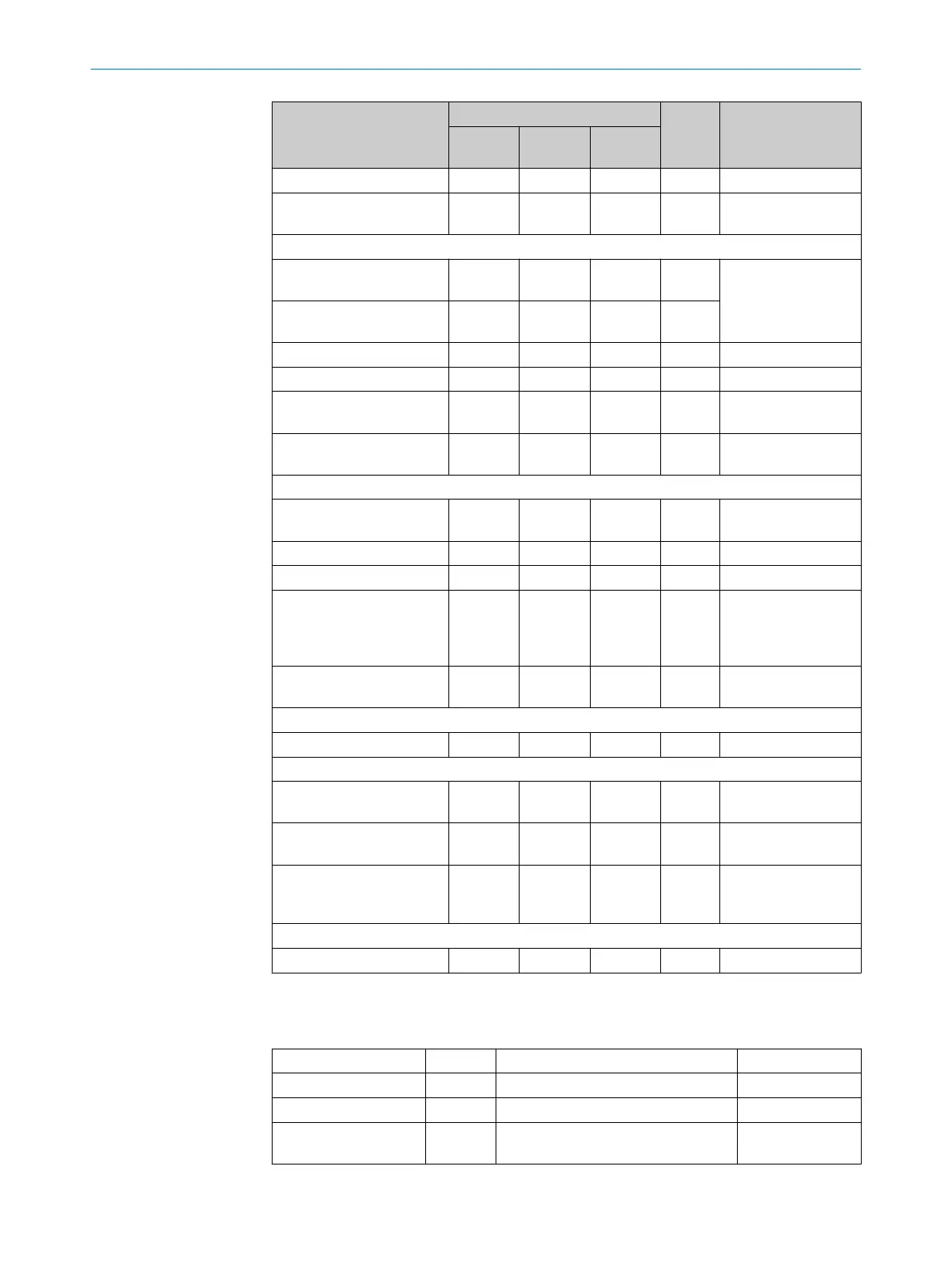

Parameter

Value

Units Remarks

Minimum Typical

Maxi‐

mum

Reset duration 0.02 0.06 µs Reset is High active

Recovery time following

communications failure

727 µs

Characteristics of the motor feedback system

Position resolution per rev‐

olution

23 40 Bit

The total can be a

maximum of 40 bit

Number of resolved revolu‐

tions

16 40 Bit

Rotation speed

262,000 rad/s 24 bit/rotation

Acceleration 670,000 rad/s² 24 bit/rotation

Dead time 10.5 µs

SYNC trigger to posi‐

tion register update

Sampling latency 1 µs

SYNC trigger to posi‐

tion sampling time

Characteristics of the host interface

Cycle time of the frequency

inverter

12.1 1,950 µs In SYNC mode

Packet cycle time 12.1 27 µs In SYNC mode

Packet cycle time 11.52 µs

Infree-running mode

Duration of the SYNC signal 0.04 µs

The SYNC signal

must be inactive for

at least 0.04 µs per

cycle.

SYNC signal jitter 26 ns

±2 System clock

cycles

Characteristics of the SPI PIPE interface

Clock of SPI PIPE 10 MHz

Characteristics of the parameter channel

Theoretical transmission

rate

166 334 kBd

Duration of access to the

communications resource

167 1,100 µs

“short message”

Duration of access to the

encoder resource

75 ms

“long message”,

including encoder

processing time

Characteristics of the SensorHub channel

Transmission rate 334 669 kBd

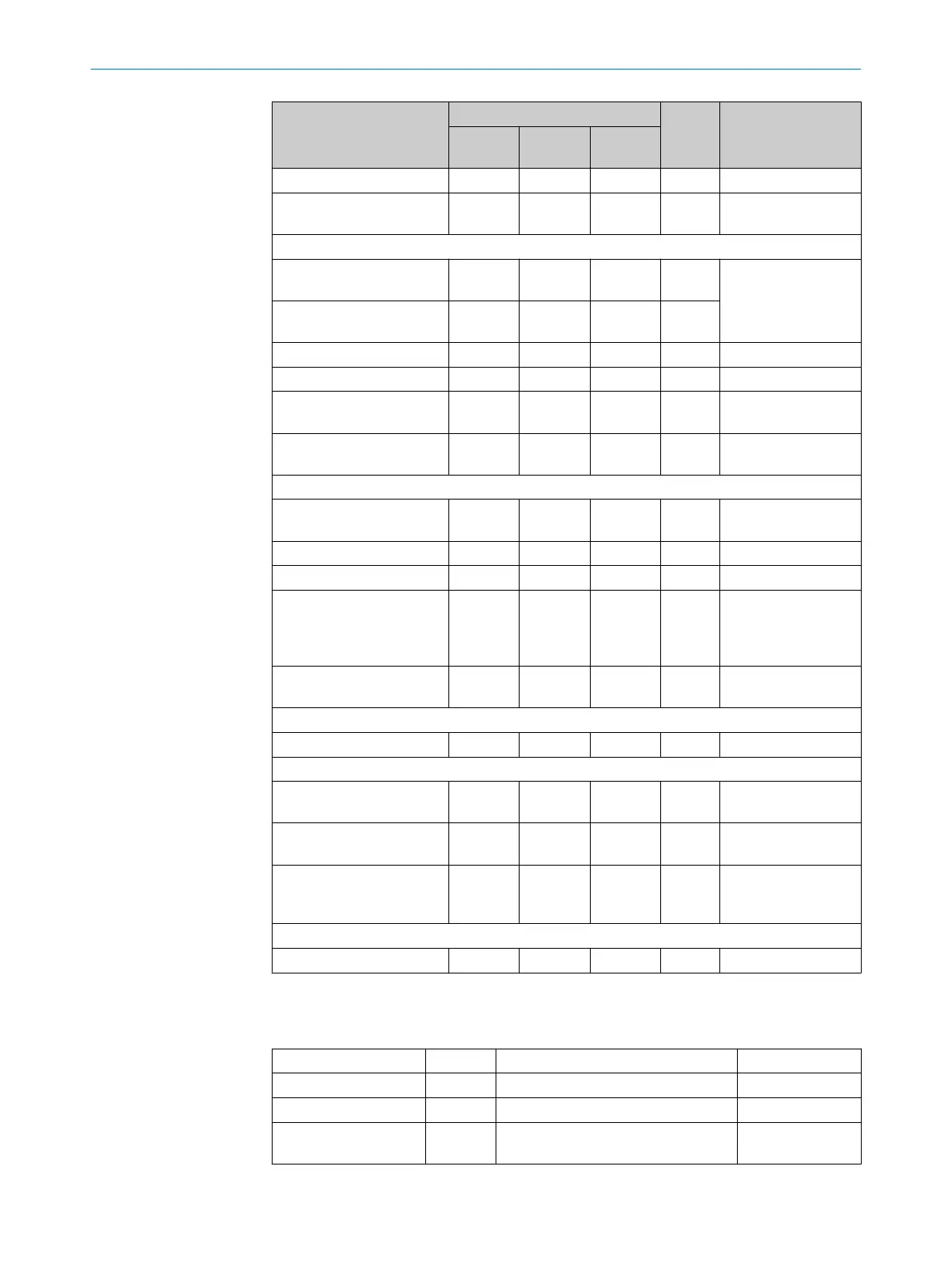

The following table contains a description of the pin functions of the DSL Master IP

Core. Pin functions

Table 186: Pin functions of the IP Core

Pin description

Type Function Note

rst Input Master reset (High active)

clk Input Clock input

sync Input Drive cycle for position sampling trig‐

ger

9 FPGA IP-CORE

138

T E C H N I C A L I N F O R M A T I O N | HIPERFACE DSL

®

8017595/ZTW6/2018-01-15 | SICK

Subject to change without notice

Loading...

Loading...