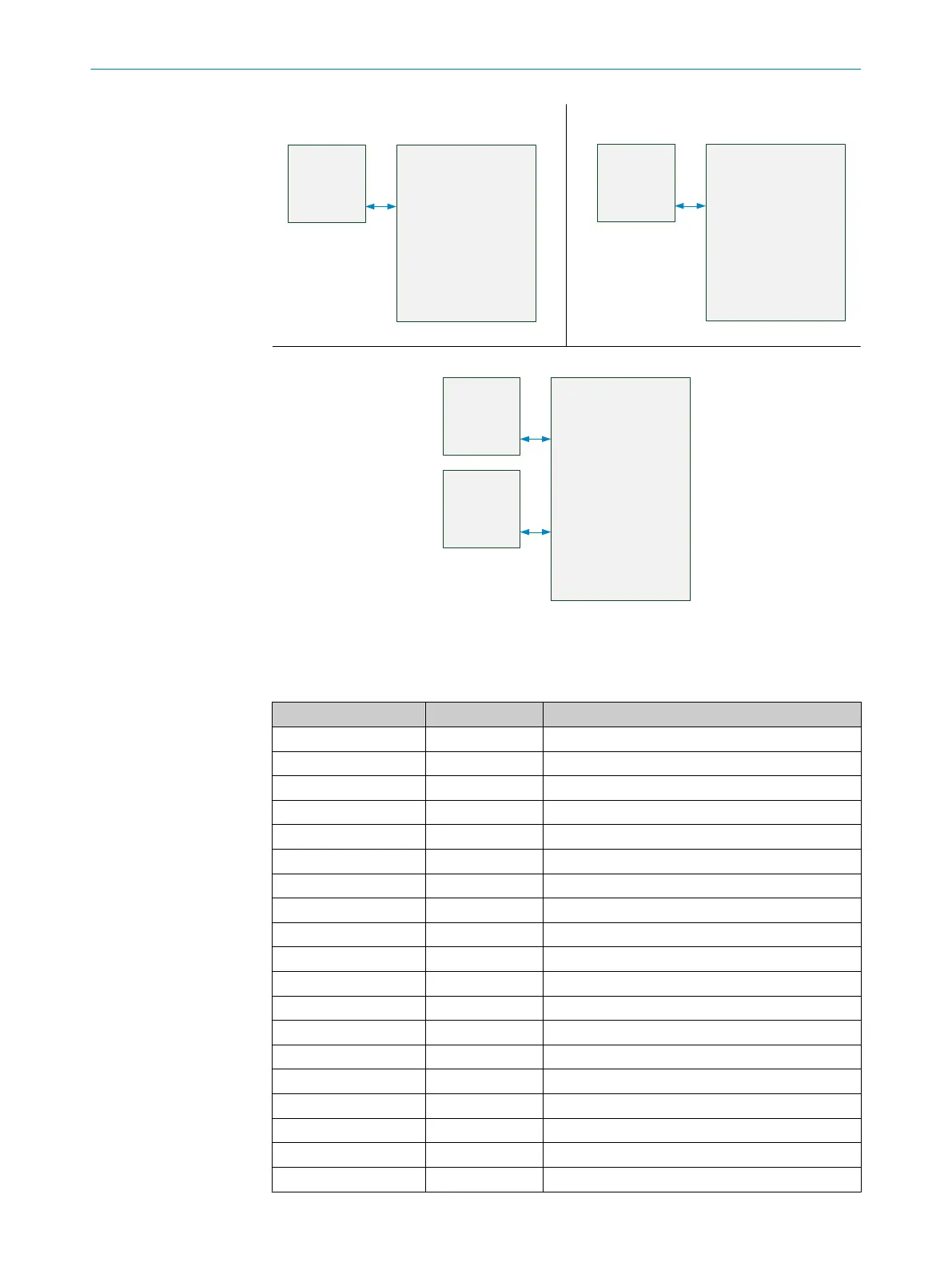

Standard DSL Master

(dslm_n)

Parallel

interface

Parallel Bus Drive interface

SPI Pipeline

Test signals

Control signals

DSL

Standard DSL Master

(dslm_n)

Serial

interface

SPI Drive interface

SPI Pipeline

Test signals

Control signals

DSL

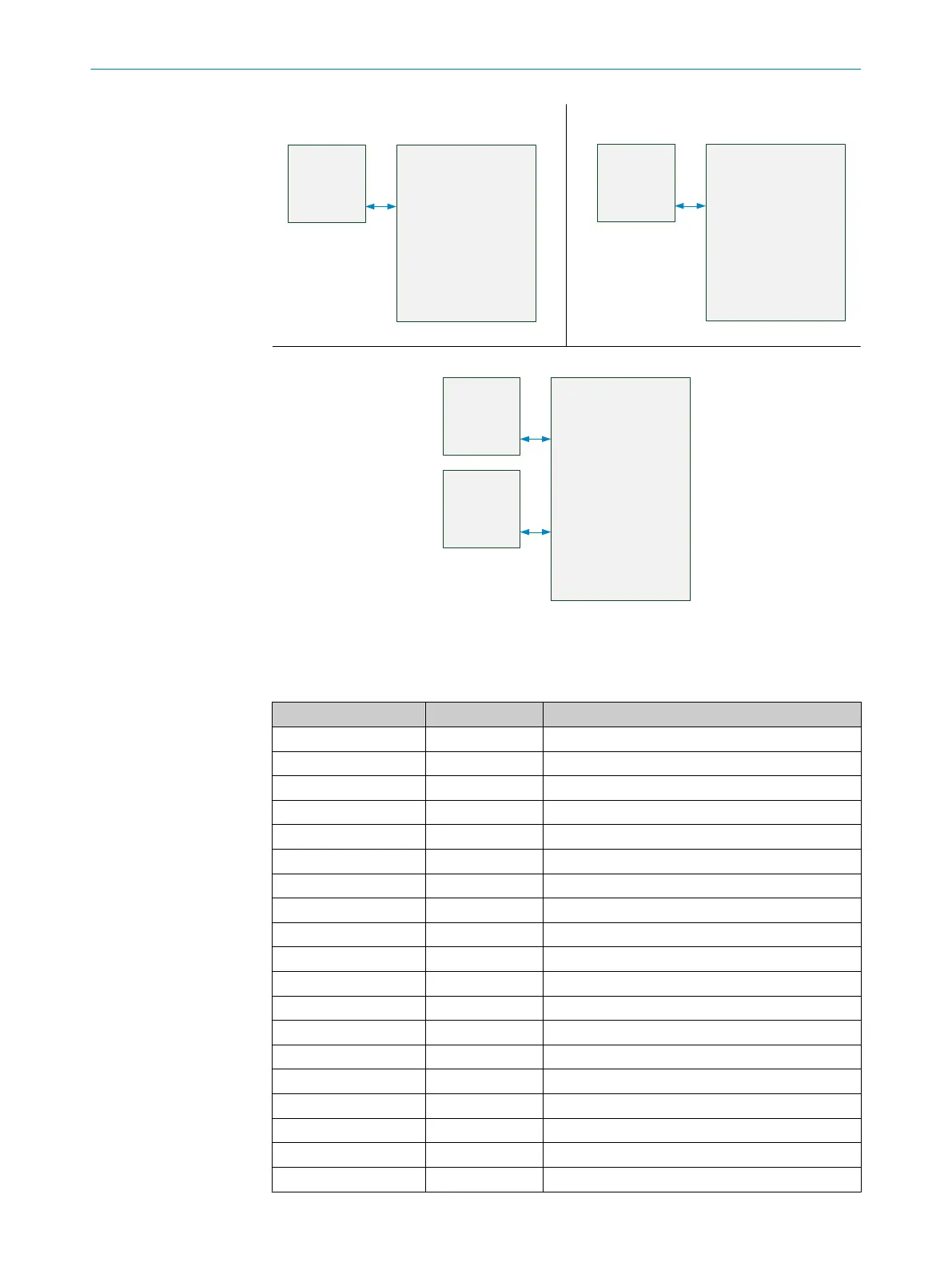

Standard DSL Master

(dslm_n)

User

interface

Miscellaneous Drive interface

SPI Pipeline

Test signals

Control signals

DSL

Serial

interface

SPI

A)

B)

C)

Figure 7: Block diagrams of the "standard" DSL Master IP Core with interfaces

4.2.1 DSL Master inputs / outputs

Table 7: Pin functions of the IP Core interface

Signal name Type Function

rst* Input Master reset (High active)

clk* Input Clock input

sync* Input Position sampling resolution

interrupt Output Configurable interrupt

link Output Connection indication

pos_ready Output Position data availability indication

sync_locked Output Position sampling resolution locked

bigend Input Byte sequence choice

fast_pos_rdy Output Fast position update indication

sample Output DSL bit sampling information

estimator_on Output Postion Estimator activated

safe_channel_err Output Transmission error in safe channel 1

safe_pos_err Output Safe position not valid

acceleration_err Output Fast channel / position error

acc_thr_err Output Fast channel / position threshold error

encoding_err Output DSL message encoding error

dev_thr_err Output Estimator deviation threshold reached

aux_signals Output (12) Auxiliary signals

dsl_in* Input DSL cable, input data

HARDWARE INSTALLATION 4

8017595/ZTW6/2018-01-15 | SICK T E C H N I C A L I N F O R M A T I O N | HIPERFACE DSL

®

19

Subject to change without notice

Loading...

Loading...