NOTE

It should be noted that apart from a reset of the Master, all system control bits can only

be set and deleted by the user.

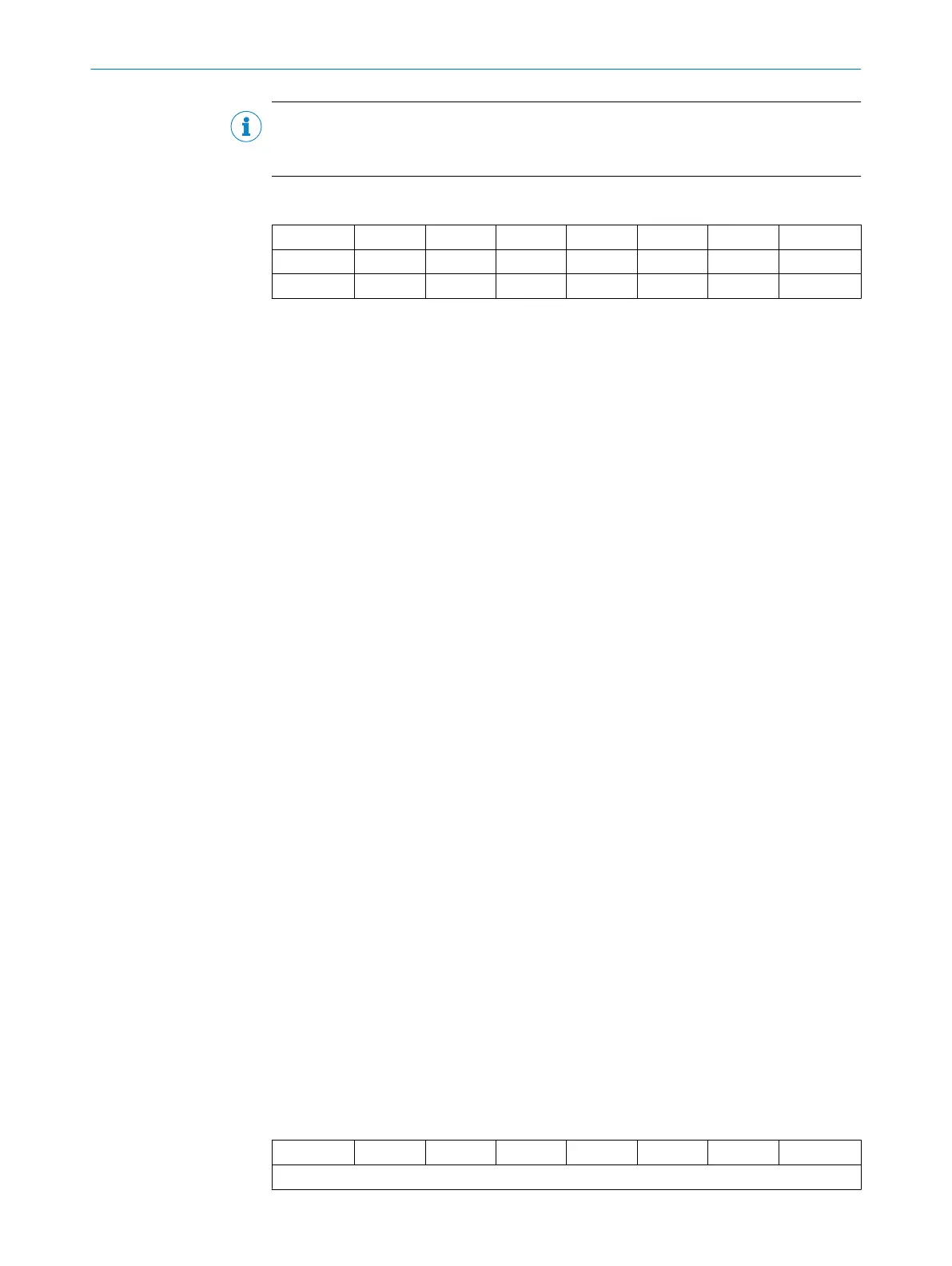

Register 00h: System control

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

PRST MRST FRST LOOP PRDY SPPE SPOL OEN

Bit 7 Bit 0

Bit 7 PRST: Protocol reset

1 = A forced reset of the protocol status will be initiated. If the bit is deleted, a restart of

the connection is triggered.

0 = Normal protocol action

Bit 6 MRST: Messages reset

1 = The Parameters Channel is reset. Current short and long messages are discarded.

0 = Normal Parameters Channel action

Bit 5

FRST: Pipeline FIFO, reset

1 = The FIFO is reset. Data is not stored and cannot be read.

0 = Normal FIFO access

Bit 4

LOOP: Test drive interface

Value for the read back test for drive interface. This value has no other purpose.

Bit 3 PRDY: POS_READY mode.

1 = pos_ready shows time of receipt of all position transmissions.

0 = pos_ready shows only the time of receipt of position transmissions following a

control clock (sync input).

Bit 2 SPPE: SPI-PIPE activation

1 = SPI-PIPE activated. Access to pipeline status and data via SPI-PIPE. The registers

PIPE_S and PIPE_D are read as "0".

0 = SPI-PIPE deactivated. Access to pipeline status and data via the registers PIPE_S

and PIPE_D.

Bit 1 SPOL: Polarity of the synchronization pulse

1 = The sync trailing edge is used.

0 = The sync leading edge is used.

Bit 0 OEN: Activation of the output

1 = The DSL cables are activated for output to the DSL Slave.

0 = The impedance of the DSL cable is high.

6.3.2 Synchronization control

The SYNC_CTRL register for control of the synchronization contains the bit with which

the synchronization source for position sampling is controlled.

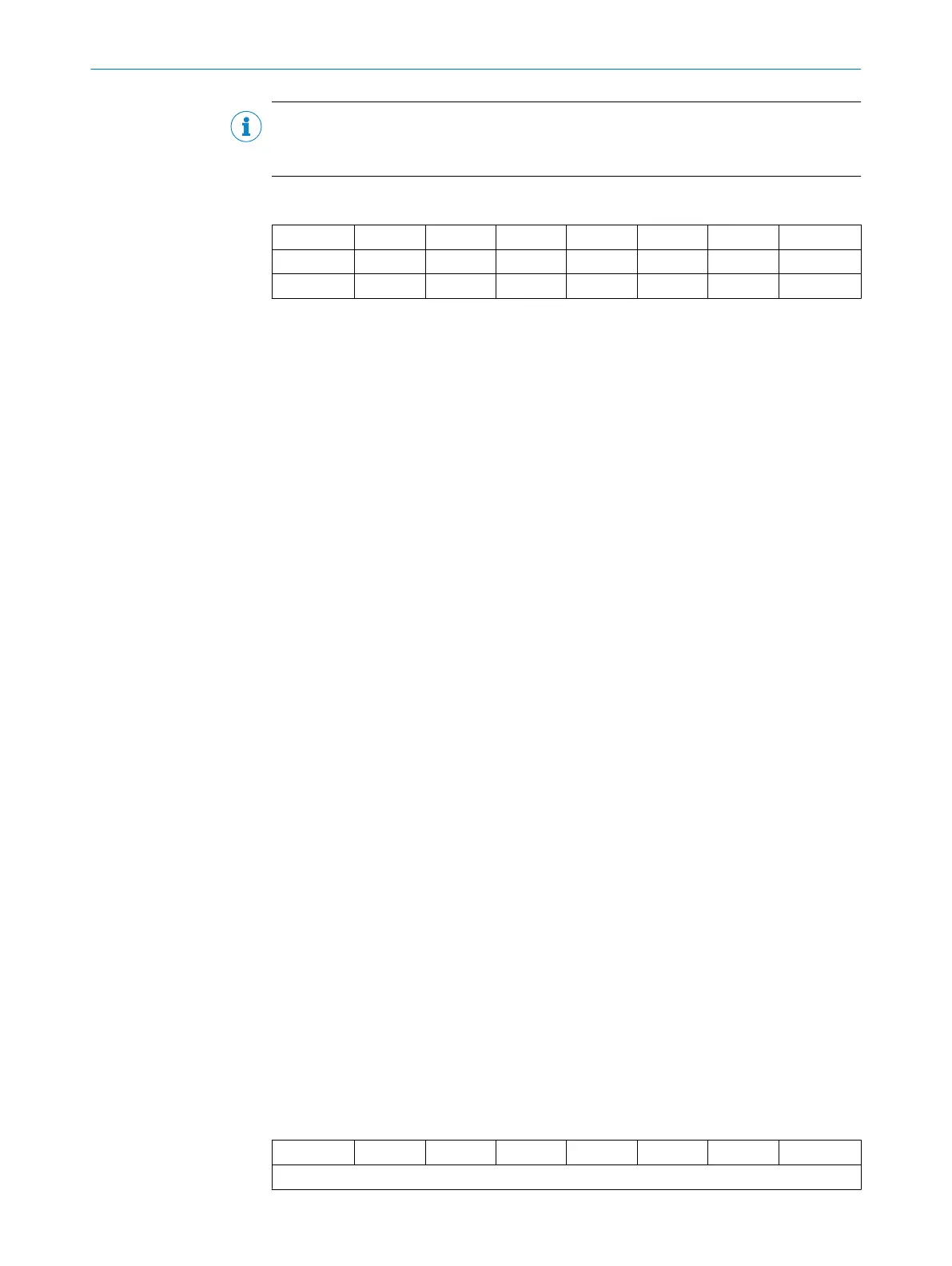

Register 01h: Synchronization control

W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-1

ES

6 REGISTER MAP

34

T E C H N I C A L I N F O R M A T I O N | HIPERFACE DSL

®

8017595/ZTW6/2018-01-15 | SICK

Subject to change without notice

Loading...

Loading...