SN8P2624

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 86 Version 0.3

9

9

9

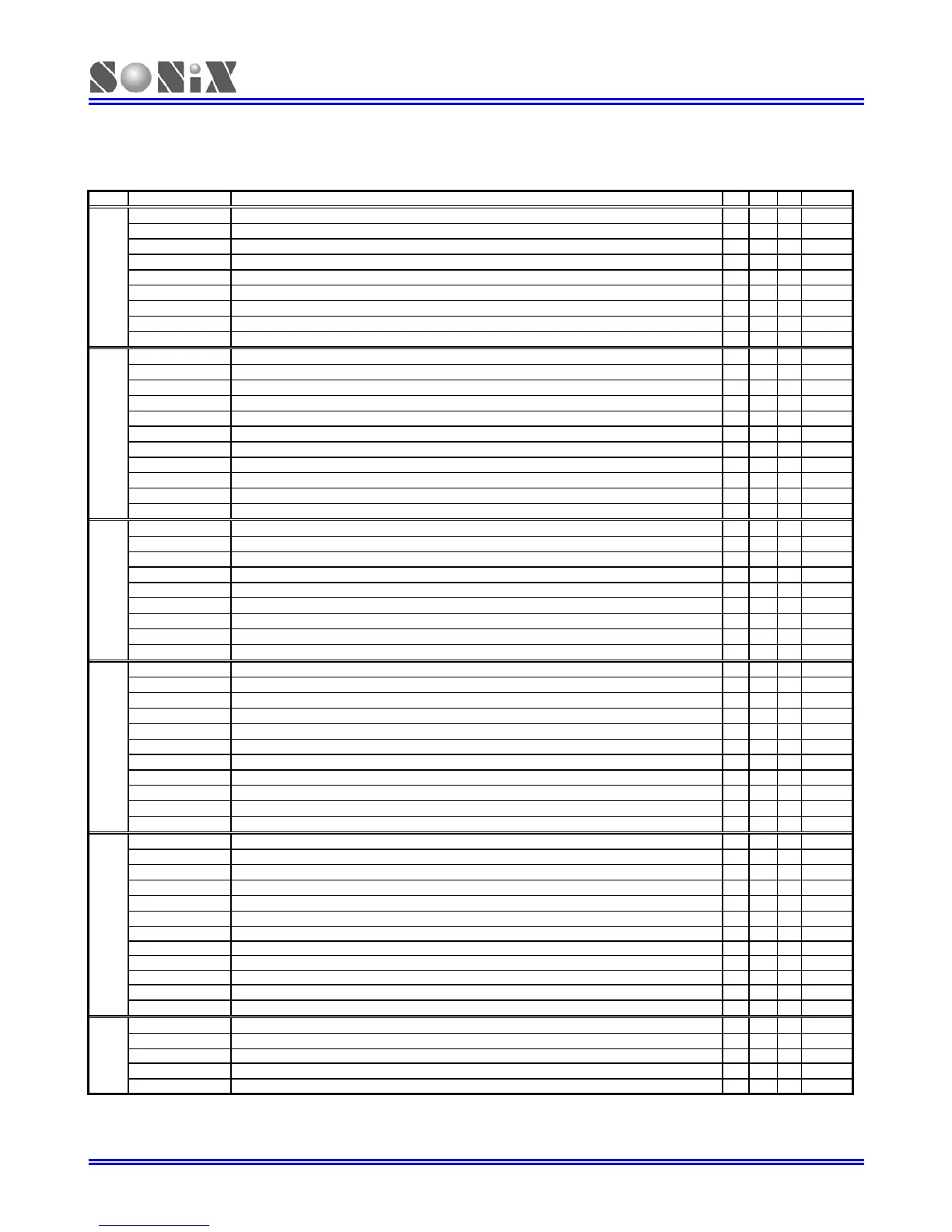

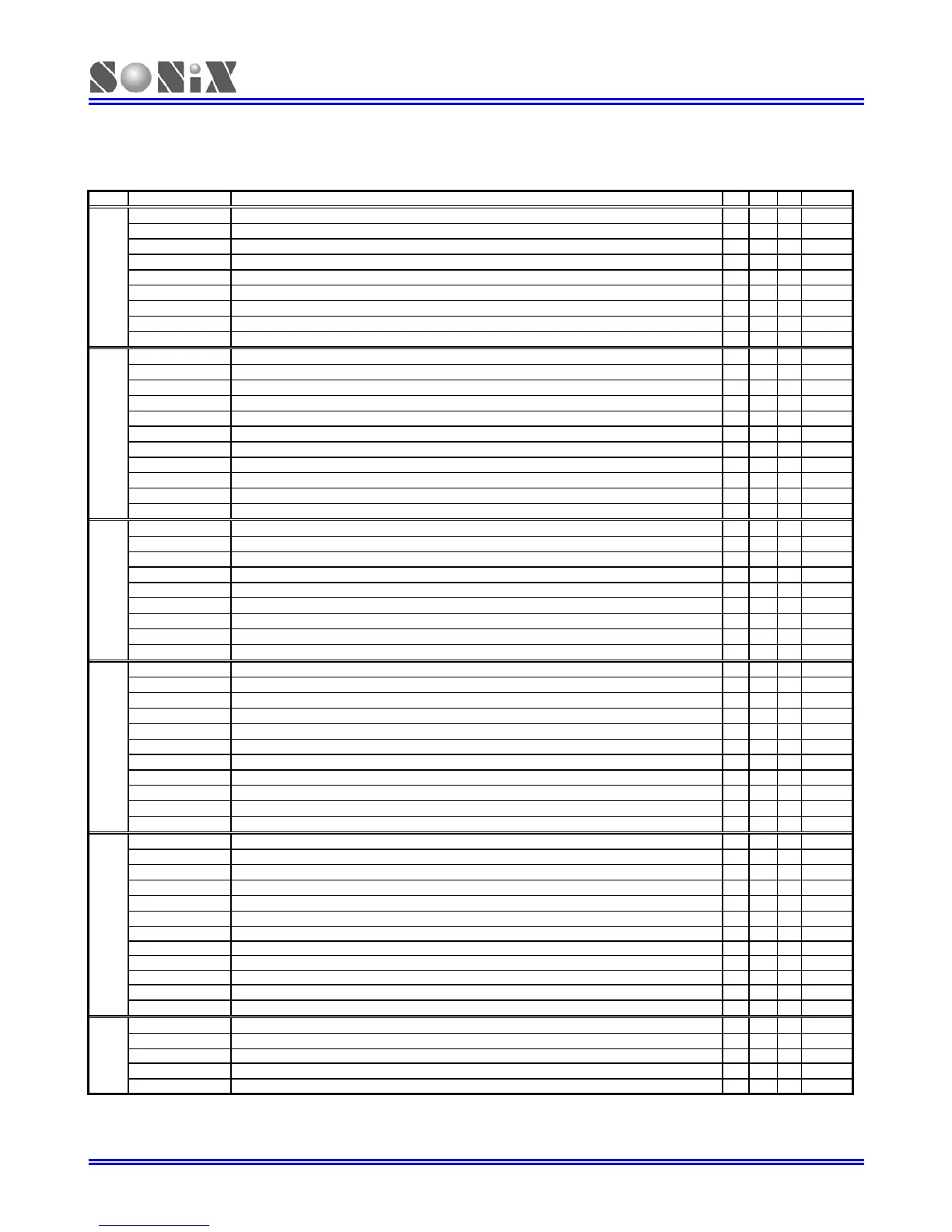

INSTRUCTION TABLE

Field Mnemonic Description C DC Z Cycle

MOV A,M

A

← M

- -

√

1

M MOV M,A

M

← A

- - - 1

O B0MOV A,M

A

← M (bank 0)

- -

√

1

V B0MOV M,A

M (bank 0)

← A

- - - 1

E MOV A,I

A

← I

- - - 1

B0MOV M,I

M

← I, “M” only supports 0x80~0x87 registers (e.g. PFLAG,R,Y,Z…)

- - - 1

XCH A,M

A

←→M

- - - 1+N

B0XCH A,M

A

←→M (bank 0)

- - - 1+N

MOVC

R, A

← ROM [Y,Z]

- - - 2

ADC A,M

A

← A + M + C, if occur carry, then C=1, else C=0

√ √ √

1

A ADC M,A

M

← A + M + C, if occur carry, then C=1, else C=0

√ √ √

1+N

R ADD A,M

A

← A + M, if occur carry, then C=1, else C=0

√ √ √

1

I ADD M,A

M

← A + M, if occur carry, then C=1, else C=0

√ √ √

1+N

T B0ADD M,A

M (bank 0)

← M (bank 0) + A, if occur carry, then C=1, else C=0

√ √ √

1+N

H ADD A,I

A

← A + I, if occur carry, then C=1, else C=0

√ √ √

1

M SBC A,M

A

← A - M - /C, if occur borrow, then C=0, else C=1

√ √ √

1

E SBC M,A

M

← A - M - /C, if occur borrow, then C=0, else C=1

√ √ √

1+N

T SUB A,M

A

← A - M, if occur borrow, then C=0, else C=1

√ √ √

1

I SUB M,A

M

← A - M, if occur borrow, then C=0, else C=1

√ √ √

1+N

C SUB A,I

A

← A - I, if occur borrow, then C=0, else C=1

√ √ √

1

AND A,M

A

← A and M

- -

√

1

L AND M,A

M

← A and M

- -

√

1+N

O AND A,I

A

← A and I

- -

√

1

G OR A,M

A

← A or M

- -

√

1

I OR M,A

M

← A or M

- -

√

1+N

C OR A,I

A

← A or I

- -

√

1

XOR A,M

A

← A xor M

- -

√

1

XOR M,A

M

← A xor M

- -

√

1+N

XOR A,I

A

← A xor I

- -

√

1

SWAP M

A (b3~b0, b7~b4)

←M(b7~b4, b3~b0)

- - - 1

P SWAPM M

M(b3~b0, b7~b4)

← M(b7~b4, b3~b0)

- - - 1+N

R RRC M

A

← RRC M

√

-- 1

O RRCM M

M

← RRC M

√

-- 1+N

C RLC M

A

← RLC M

√

-- 1

E RLCM M

M

← RLC M

√

-- 1+N

S CLR M

M

← 0

- - - 1

S BCLR M.b

M.b

← 0

- - - 1+N

BSET M.b

M.b

← 1

- - - 1+N

B0BCLR M.b

M(bank 0).b

← 0

- - - 1+N

B0BSET M.b

M(bank 0).b

← 1

- - - 1+N

CMPRS A,I

ZF,C

← A - I, If A = I, then skip next instruction

√

-

√

1 + S

B CMPRS A,M

ZF,C

← A – M, If A = M, then skip next instruction

√

-

√

1 + S

R INCS M

A

← M + 1, If A = 0, then skip next instruction

- - - 1+ S

A INCMS M

M

← M + 1, If M = 0, then skip next instruction

- - - 1+N+S

N DECS M

A

← M - 1, If A = 0, then skip next instruction

- - - 1+ S

C DECMS M

M

← M - 1, If M = 0, then skip next instruction

- - - 1+N+S

H BTS0 M.b If M.b = 0, then skip next instruction - - - 1 + S

BTS1 M.b If M.b = 1, then skip next instruction - - - 1 + S

B0BTS0 M.b If M(bank 0).b = 0, then skip next instruction - - - 1 + S

B0BTS1 M.b If M(bank 0).b = 1, then skip next instruction - - - 1 + S

JMP d

PC15/14

← RomPages1/0, PC13~PC0 ← d

- - - 2

CALL d

Stack

← PC15~PC0, PC15/14 ← RomPages1/0, PC13~PC0 ← d

- - - 2

M RET

PC

← Stack

- - - 2

I RETI

PC

← Stack, and to enable global interrupt

- - - 2

S PUSH To push ACC and PFLAG (except NT0, NPD bit) into buffers. - - - 1

C

POP To pop ACC and PFLAG (except NT0, NPD bit) from buffers.

√ √ √

1

NOP No operation - - - 1

Note: 1. “M” is system register or RAM. If “M” is system registers then “N” = 0, otherwise “N” = 1.

2. If branch condition is true then “S = 1”, otherwise “S = 0”.

Loading...

Loading...