The Cortex-M4 processor PM0214

36/262 PM0214 Rev 9

2.2.8 Programming hints for the synchronization primitives

ISO/IEC C cannot directly generate the exclusive access instructions. CMSIS provides

intrinsic functions for generation of these instructions:

For example:

uint16_t value;

uint16_t *address = 0x20001002;

value = __LDREXH (address); // load 16-bit value from memory address

//0x20001002

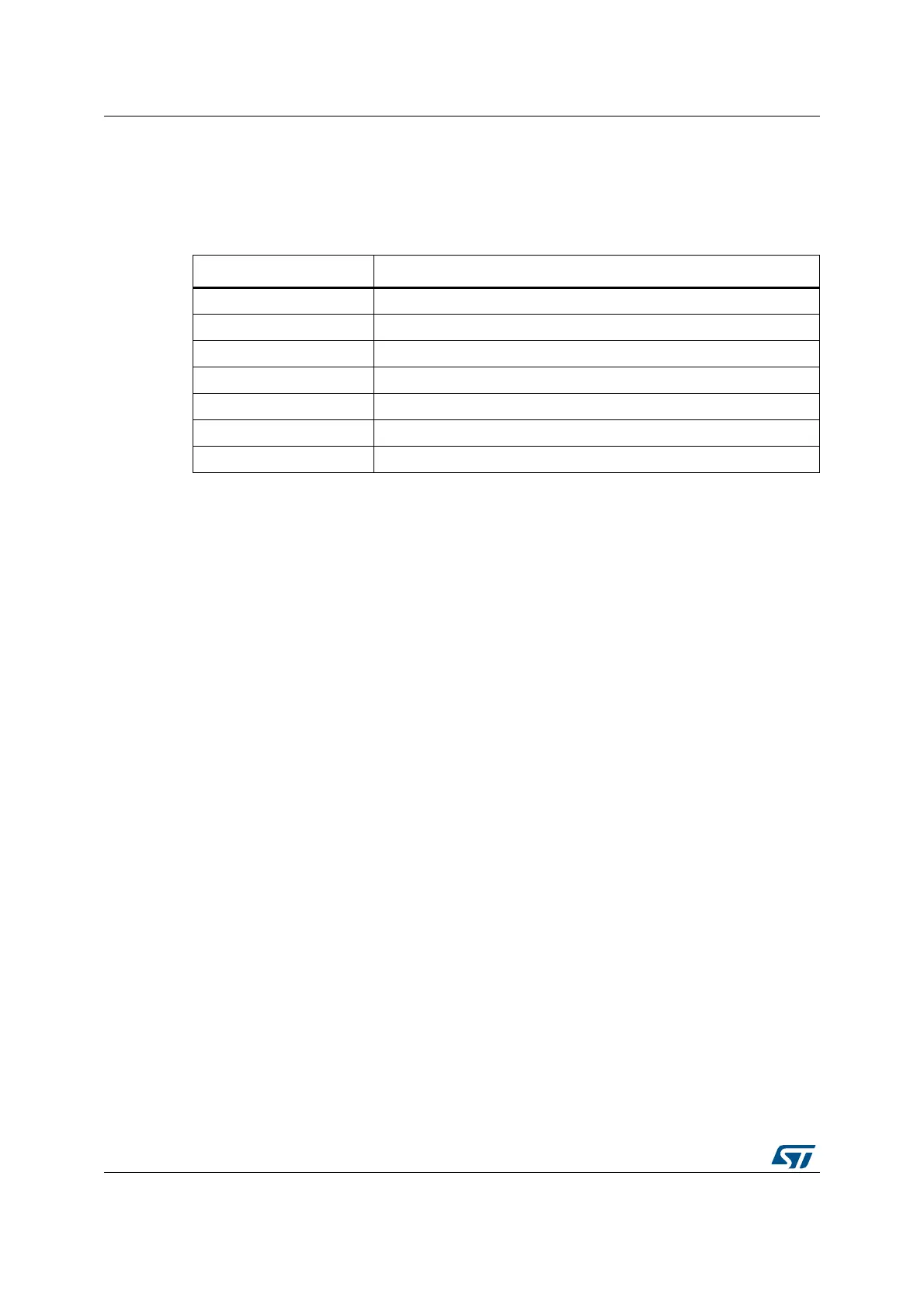

Table 16. CMSIS functions for exclusive access instructions

Instruction CMSIS function

LDREX uint32_t __LDREXW (uint32_t *addr)

LDREXH uint16_t __LDREXH (uint16_t *addr)

LDREXB uint8_t __LDREXB (uint8_t *addr)

STREX uint32_t __STREXW (uint32_t value, uint32_t *addr)

STREXH uint32_t __STREXH (uint16_t value, uint16_t *addr)

STREXB uint32_t __STREXB (uint8_t value, uint8_t *addr)

CLREX void __CLREX (void)

Loading...

Loading...