The STM32 Cortex-M4 instruction set PM0214

58/262 PM0214 Rev 9

3.2 CMSIS intrinsic functions

ISO/IEC C code cannot directly access some Cortex-M4 instructions. This section describes

intrinsic functions that can generate these instructions, provided by the CMIS, and that

might be provided by a C compiler. If a C compiler does not support an appropriate intrinsic

function, you might have to use an inline assembler to access some instructions.

The CMSIS provides the intrinsic functions listed in Table 22 to generate instructions that

ANSI cannot directly access.

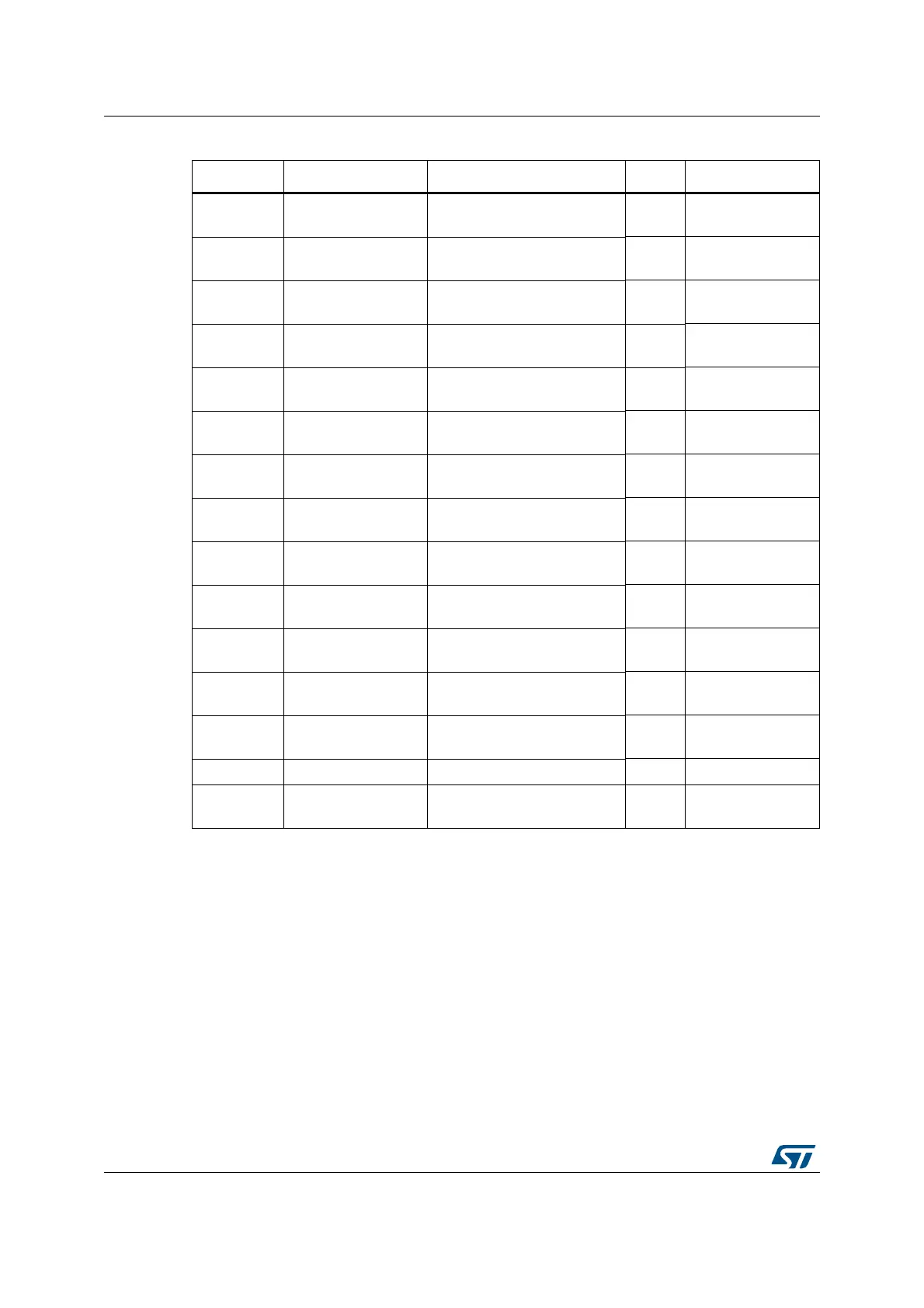

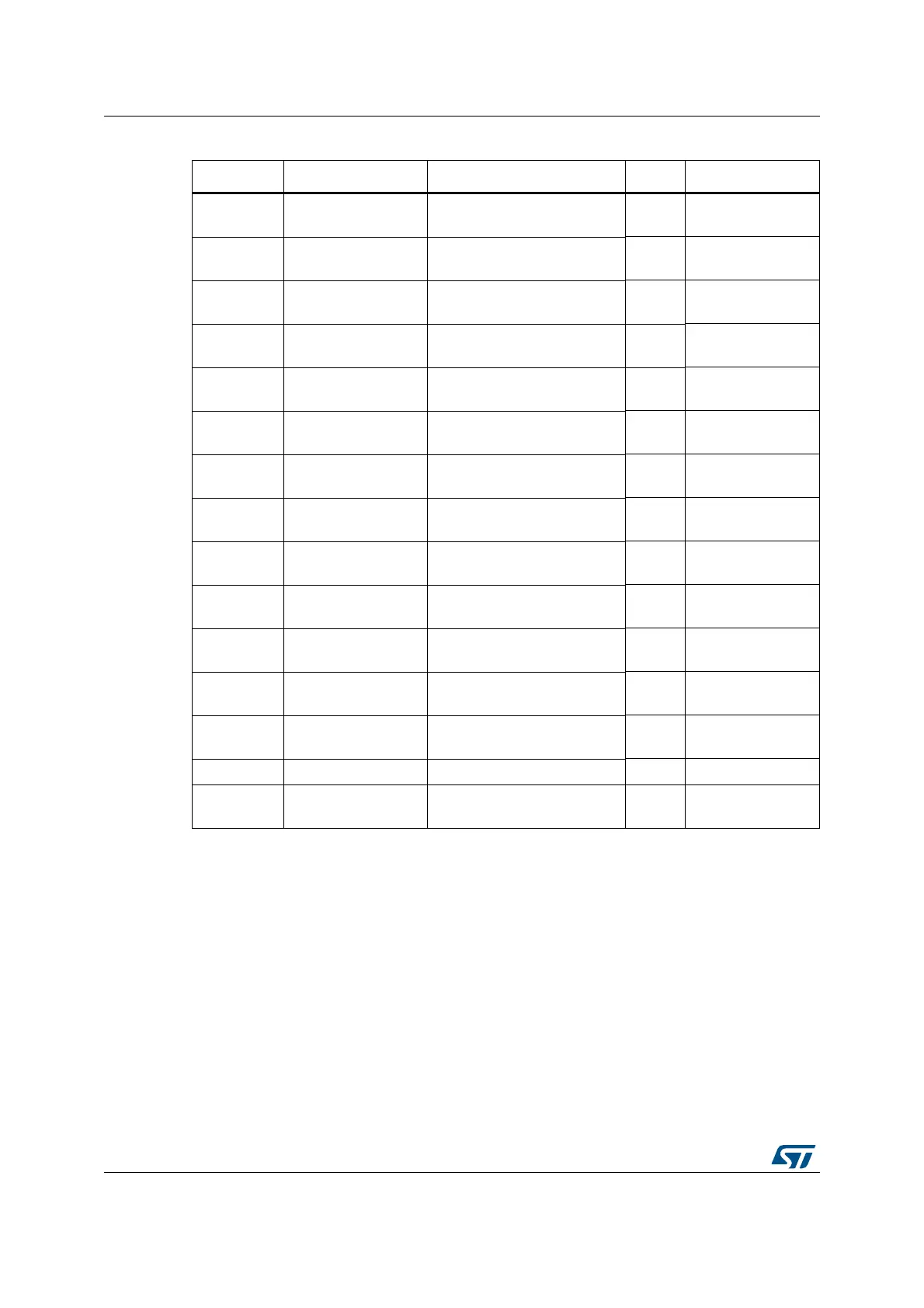

VMOV Dd[x], Rt

Copy Arm core register to

scalar

—

3.10.15 on page

165

VMOV Rt, Dn[x]

Copy scalar to Arm core

register

—

3.10.16 on page

166

VMRS Rt, FPSCR

Move FPSCR to Arm core

register or APSR

N,Z,C,V

3.10.19 on page

169

VMSR FPSCR, Rt

Move to FPSCR from Arm

Core register

FPSCR

3.10.20 on page

170

VMUL.F32 {Sd,} Sn, Sm Floating-point multiply —

3.10.21 on page

171

VNEG.F32 Sd, Sm Floating-point negate —

3.10.22 on page

172

VNMLA.F32 Sd, Sn, Sm

Floating-point multiply and

add

—

3.10.23 on page

173

VNMLS.F32 Sd, Sn, Sm

Floating-point multiply and

subtract

—

3.10.23 on page

173

VNMUL {Sd,} Sn, Sm Floating-point multiply —

3.10.23 on page

173

VPOP list Pop extension registers —

3.10.24 on page

174

VPUSH list Push extension registers —

3.10.25 on page

175

VSQRT.F32 Sd, Sm

Calculates floating-point

square root

—

3.10.26 on page

176

VSTM Rn{!}, list

Floating-point register store

multiple

—

3.10.27 on page

177

WFE — Wait for event — 3.11.11 on page 191

WFI — Wait for interrupt —

3.11.12 on page

192

Table 21. Cortex-M4 instructions (continued)

Mnemonic Operands Brief description Flags Page

Loading...

Loading...