Core peripherals PM0214

230/262 PM0214 Rev 9

4.4.6 System control register (SCR)

Address offset: 0x10

Reset value: 0x0000 0000

Required privilege: Privileged

The SCR controls features of entry to and exit from low power state.

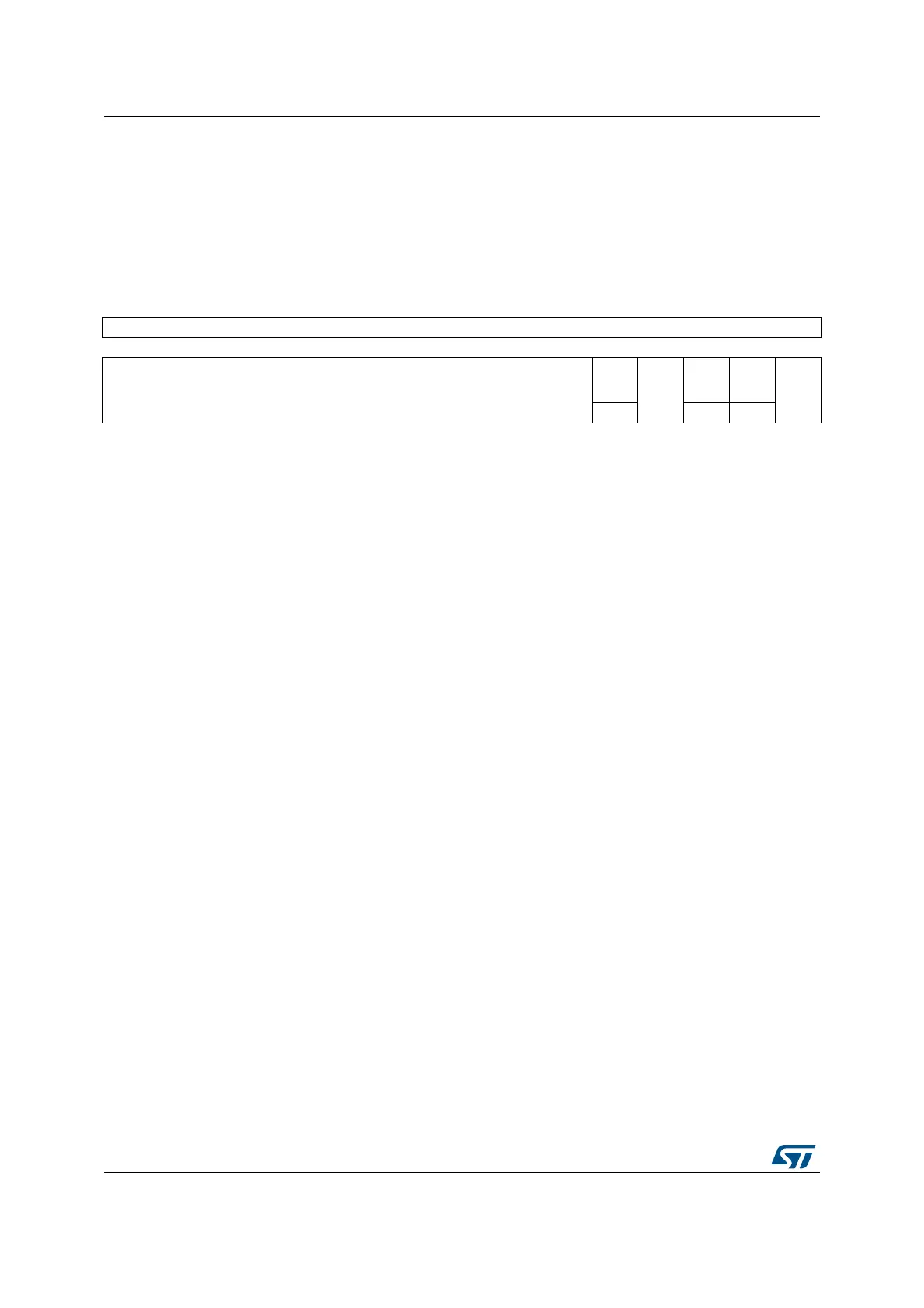

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

1514131211109876543210

Reserved

SEVON

PEND

Res.

SLEEP

DEEP

SLEEP

ON

EXIT

Res.

rw rw rw

Bits 31:5 Reserved, must be kept cleared

Bit 4 SEVEONPEND Send Event on Pending bit

When an event or interrupt enters pending state, the event signal wakes up the processor from

WFE. If the processor is not waiting for an event, the event is registered and affects the next

WFE.

The processor also wakes up on execution of an SEV instruction or an external event

0: Only enabled interrupts or events can wakeup the processor, disabled interrupts are

excluded

1: Enabled events and all interrupts, including disabled interrupts, can wakeup the

processor.

Bit 3 Reserved, must be kept cleared

Bit 2 SLEEPDEEP

Controls whether the processor uses sleep or deep sleep as its low power mode:

0: Sleep

1: Deep sleep.

Bit 1 SLEEPONEXIT

Configures sleep-on-exit when returning from Handler mode to Thread mode. Setting this bit to

1 enables an interrupt-driven application to avoid returning to an empty main application.

0: Do not sleep when returning to Thread mode.

1: Enter sleep, or deep sleep, on return from an interrupt service routine.

Bit 0 Reserved, must be kept cleared

Loading...

Loading...