Clocks AN4661

24/54 DocID027559 Rev 5

3 Clocks

Three different clock sources can be used to drive the system clock (SYSCLK):

• HSI oscillator clock.

• HSE oscillator clock.

• Main PLL (PLL) clock.

The devices have the two following secondary clock sources:

• 32 kHz low-speed internal RC (LSI RC) which drives the independent watchdog and,

optionally, the RTC used for Auto-wakeup from the Stop/Standby mode.

• 32.768 kHz low-speed external crystal (LSE crystal) which optionally drives the RTC

clock (RTCCLK).

Each clock source can be switched on or off independently when it is not used, to optimize

power consumption.

Refer to the RM0385 reference manual for the description of the clock tree.

3.1 HSE OSC clock

The high speed external clock signal (HSE) can be generated from two possible clock

sources:

• HSE external user clock (see Figure 16).

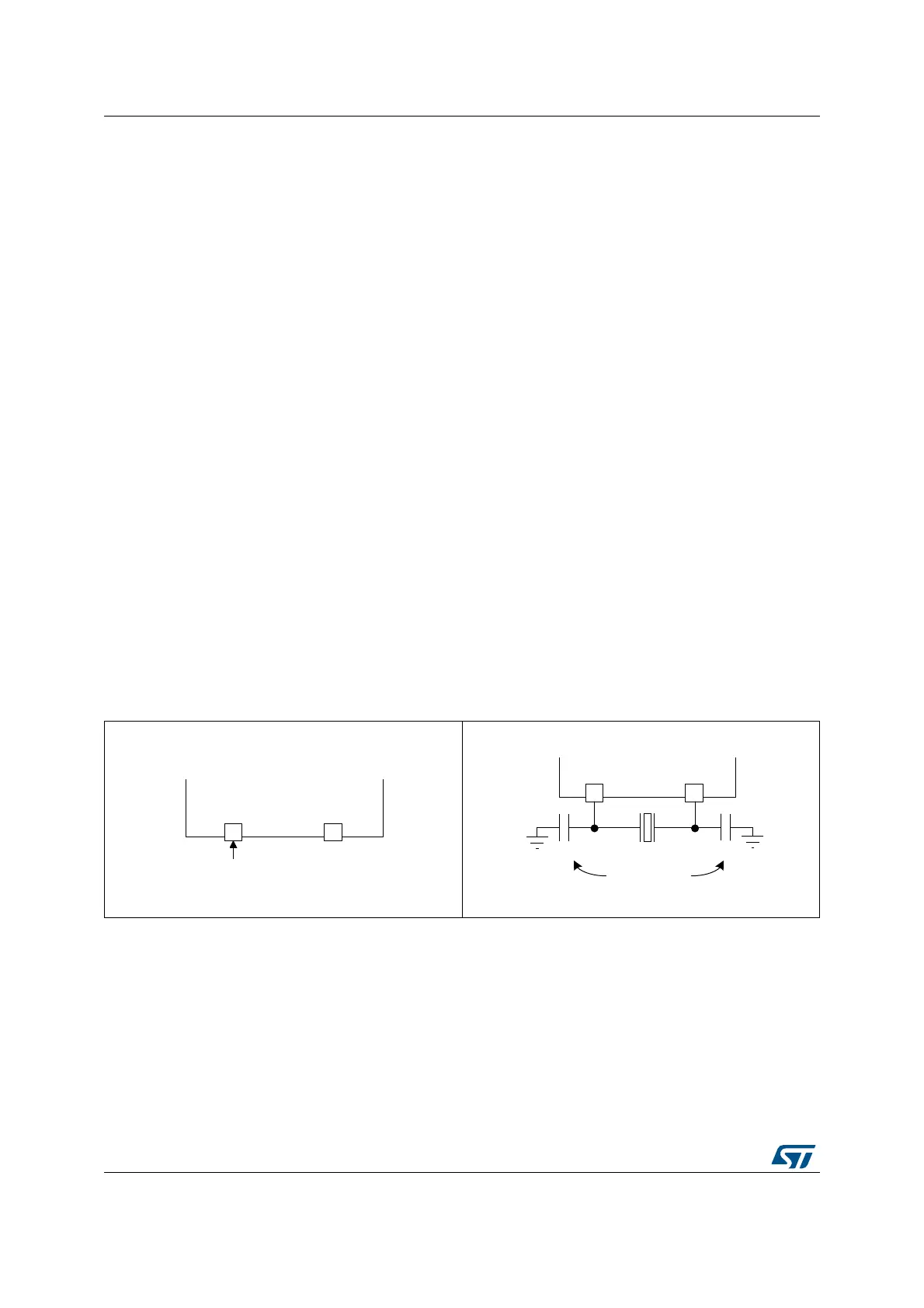

• HSE external crystal/ceramic resonator (see Figure 17).

The resonator and the load capacitors have to be placed as close as possible to the

oscillator pins in order to minimize the output distortion and startup stabilization time. The

loading capacitance values must be adjusted according to the selected oscillator.

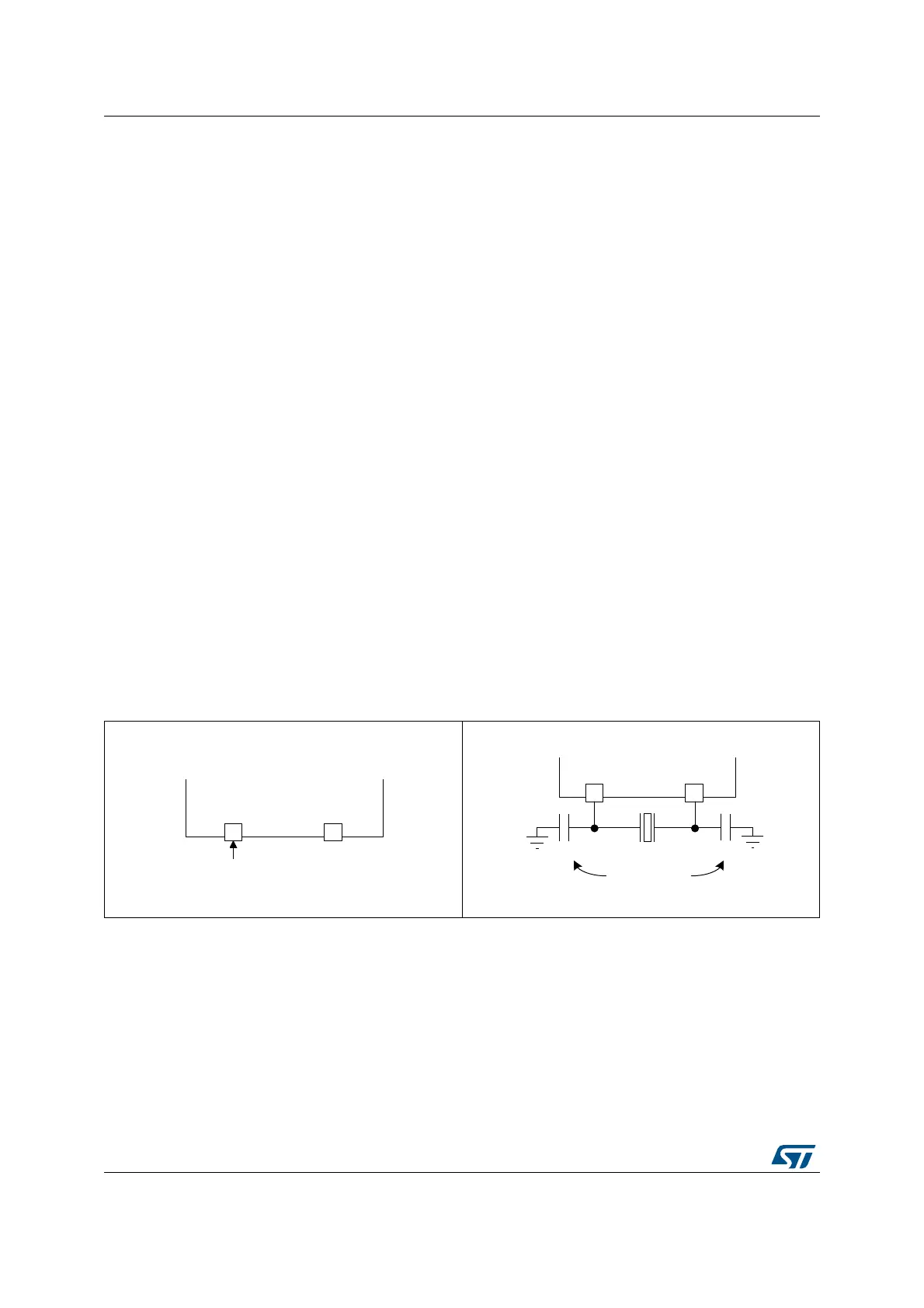

3.1.1 External user clock (HSE bypass)

In this mode, an external clock source must be provided. The user selects this mode by

setting the HSEBYP and HSEON bits in the RCC clock control register (RCC_CR). The

external clock signal (square, sinus or triangle) with ~50% duty cycle has to drive the

OSC_IN pin while the OSC_OUT pin should be left HI-Z.

Figure 16. HSE external clock Figure 17. HSE crystal/ceramic resonators

06Y9

26&B,1 26&B287

+,=

([WHUQDO

VRXUFH

06Y9

26&B,1 26&B287

&/

&/

/RDG

FDSDFLWRUV

Loading...

Loading...