99

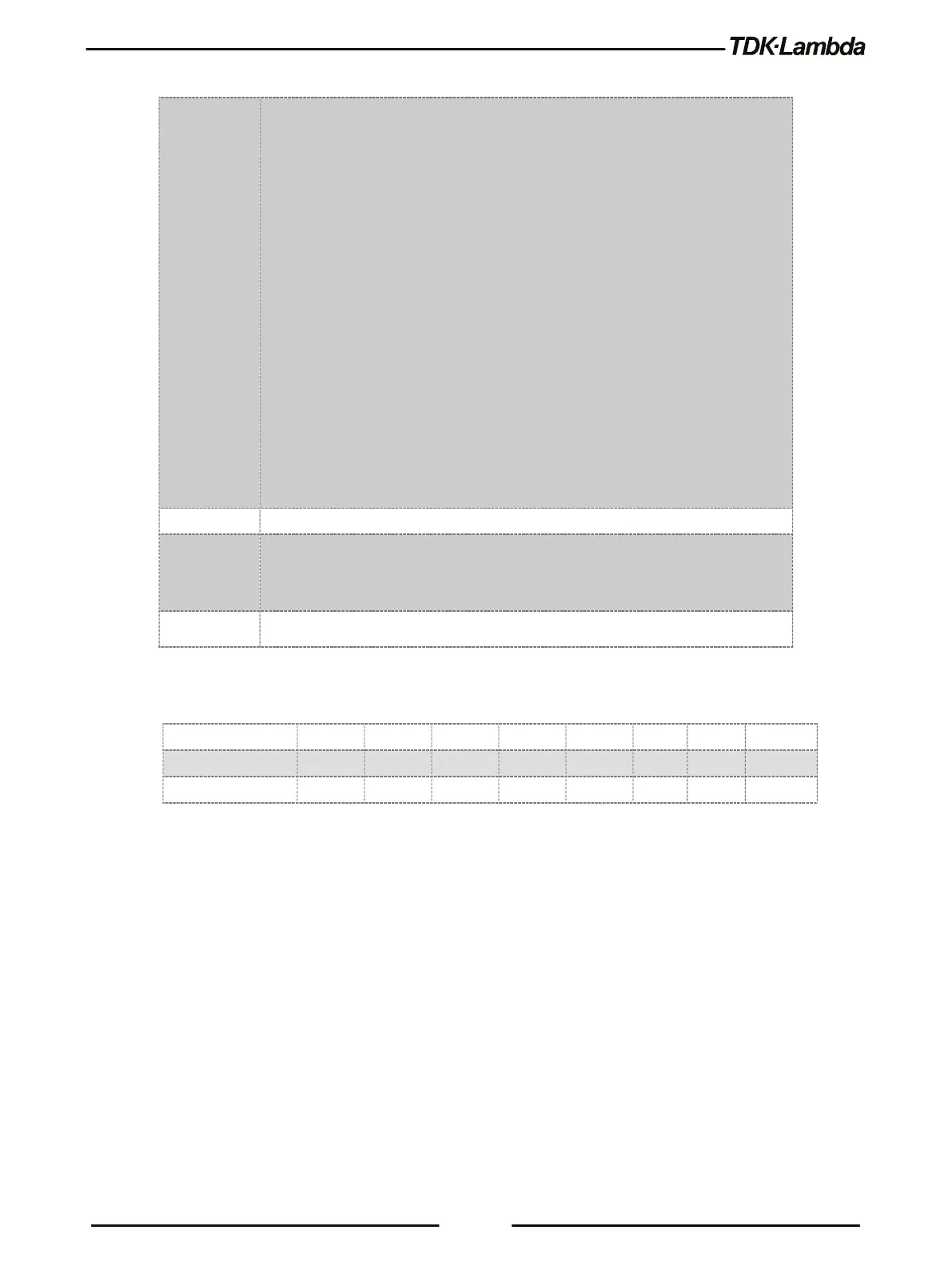

*ESE <NR1>

Function This command programs the Standard

Event Status Enable register bits. The programming determines which events of

the Standard Event Status Event register (see *ESR? below) are allowed to set

the ESB (Event Summary Bit) of the Status Byte register.

"1" in the bit position enables the corresponding event.

All of the enabled events of the Standard Event Status Event Register are

logically OR-ed to cause the Event Summary Bit (ESB) of the Status Byte

Register to be set.

• Use *PSC to control whether the Standard Event Status Enable register is

cleared at AC power on. For example, *PSC 0 preserves the Standard Event

Status Enable register contents through power cycles.

• The *CLS (clear status) command does not clear the Standard Event Status

Enable register.

• Any or all conditions can be reported to the Standard Event summary bit

through the enable register. To set the enable register mask, write a

decimal value to the register using *ESE.

0…255

Query

*ESE?

Reads Standard Event Status Enable register and returns a decimal value, which

corresponds to the binary-weighted sum of all bits set in the Standard Event

<NR1> 0…255

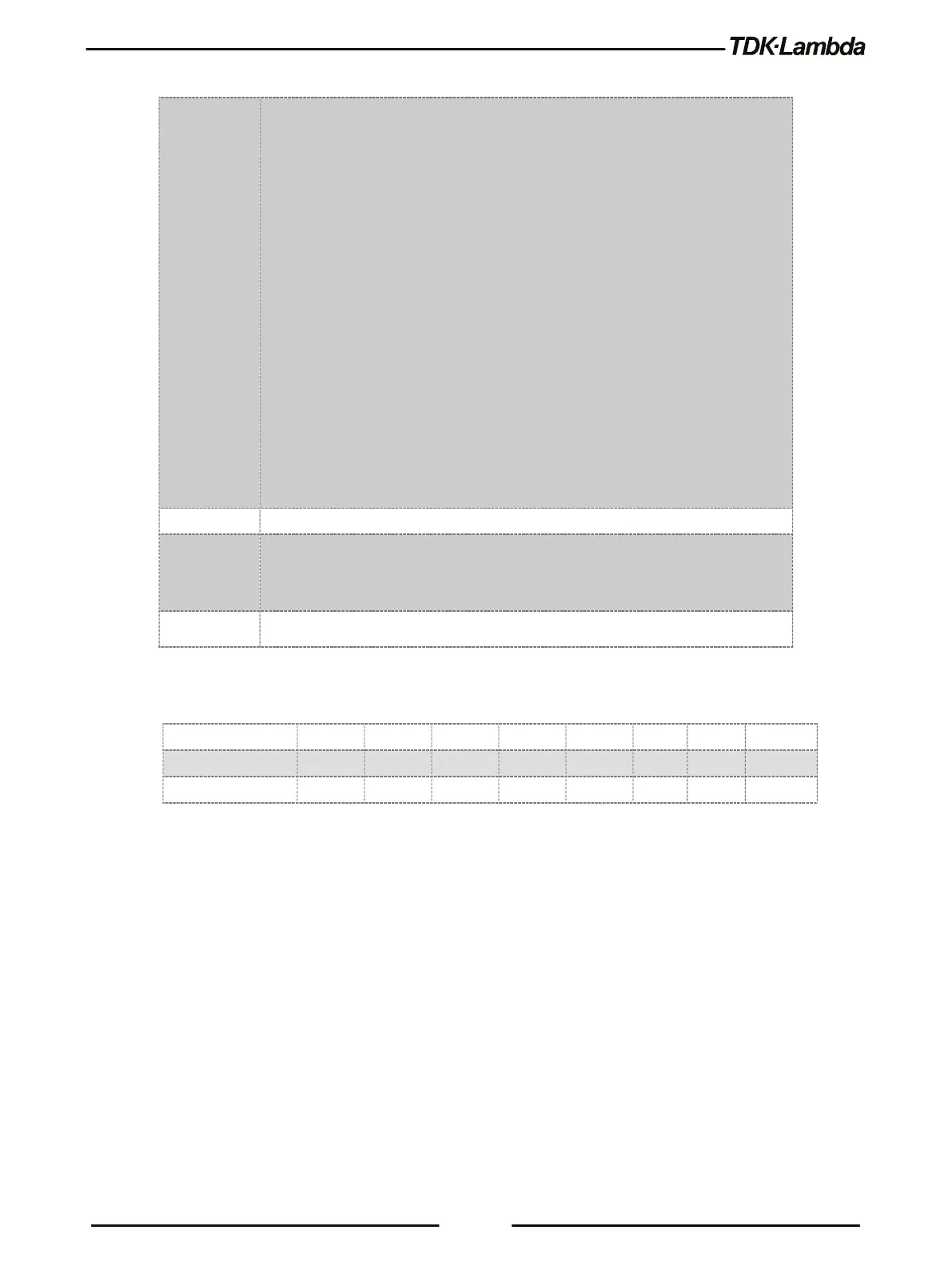

ESE Register Bit Configuration:

PON = Power On, CME = Command Error, EXE = Execution Error, DDE = Device Dependent

Error; QYE = Query Error; OPC = Operation Complete.

Loading...

Loading...