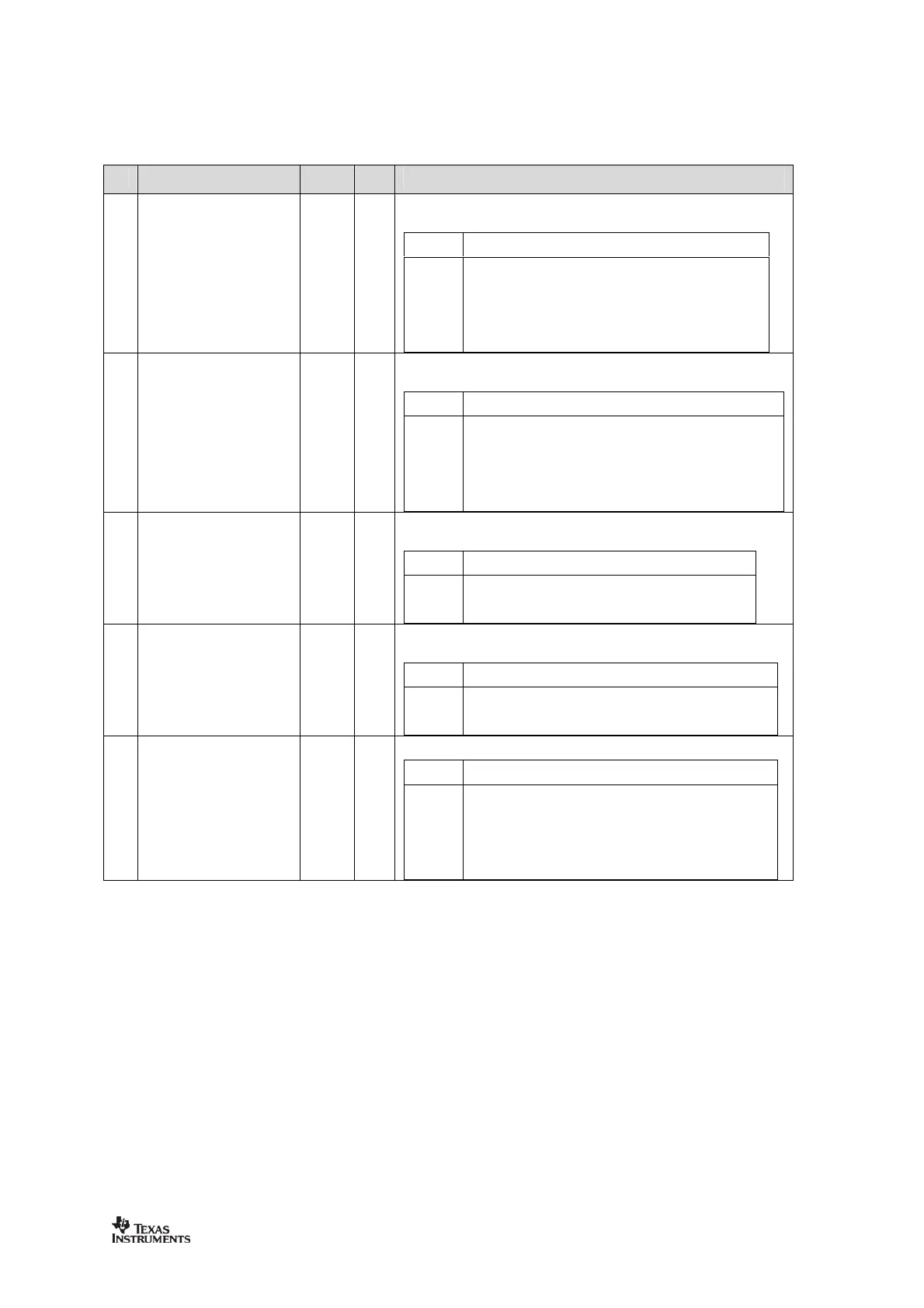

The clock recovery feedback loop integral gain to be used before a

rd is detected (used to correct offsets in data rate):

Clock recovery loop integral gain before sync word

The clock recovery feedback loop proportional gain to be used

before a sync word is detected.

Clock recovery loop proportional gain before sync word

The clock recovery feedback loop integral gain to be used after a

Clock recovery loop integral gain after sync word

The clock recovery feedback loop proportional gain to be used after

Clock recovery loop proportional gain after sy

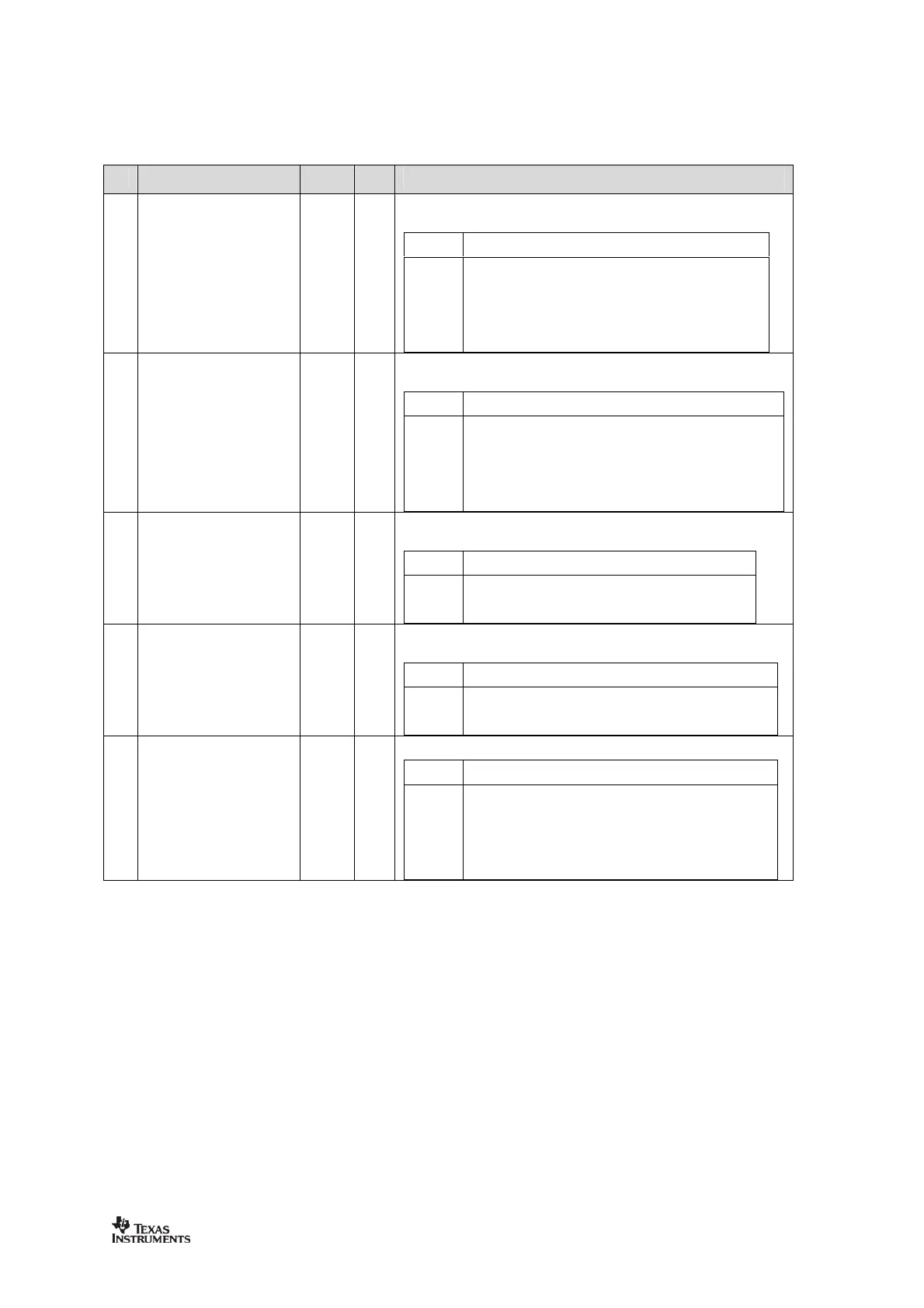

The saturation point for the data rate offset compensation algorithm:

Data rate offset saturation (max data rate difference)

No data rate offset compensation performed

Loading...

Loading...