12

Chapter 3: The TI-89 / TI-92 Plus Hardware Overview

TI

-

89 / TI

-

92 Plus Developer Guide

Not for Distribution

Beta Version January 26, 2001

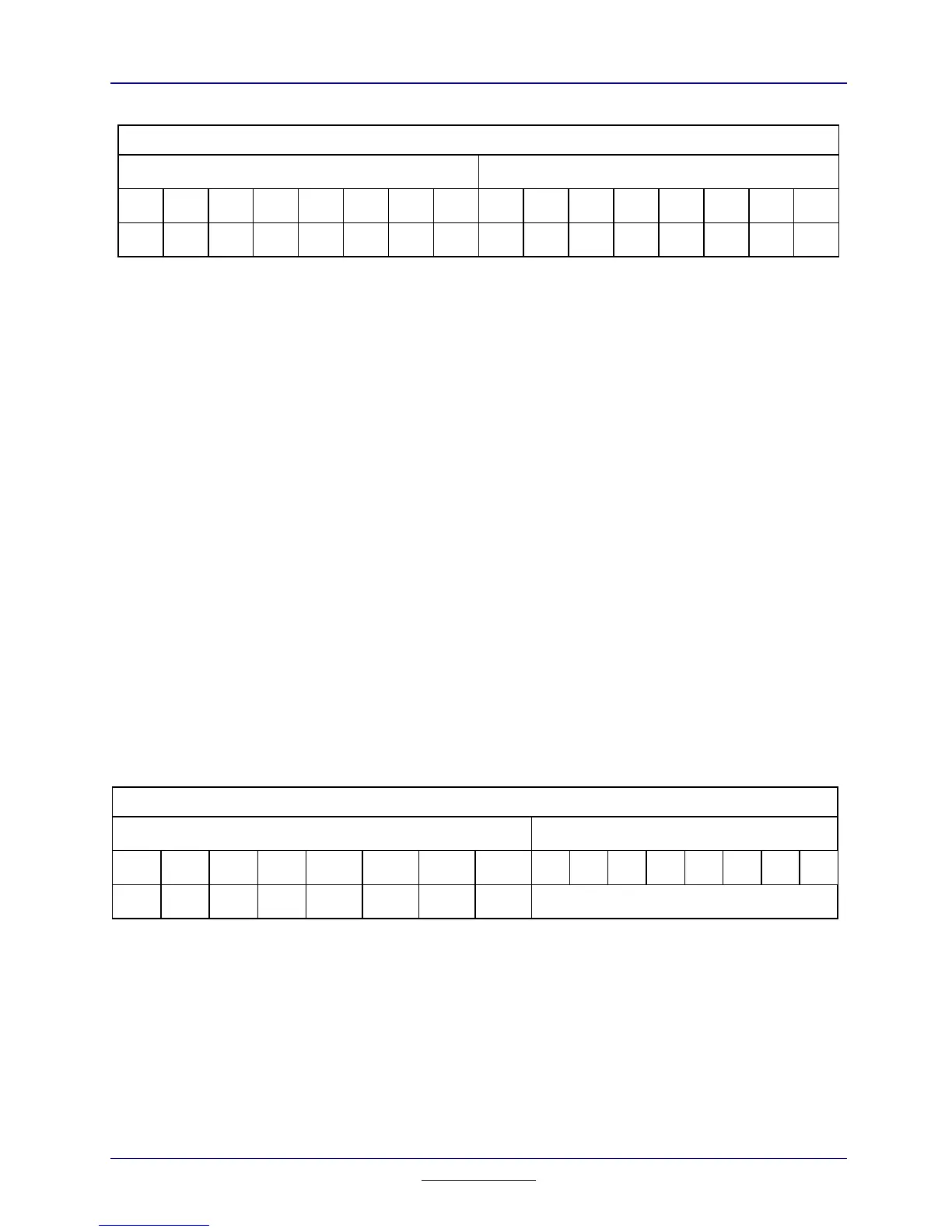

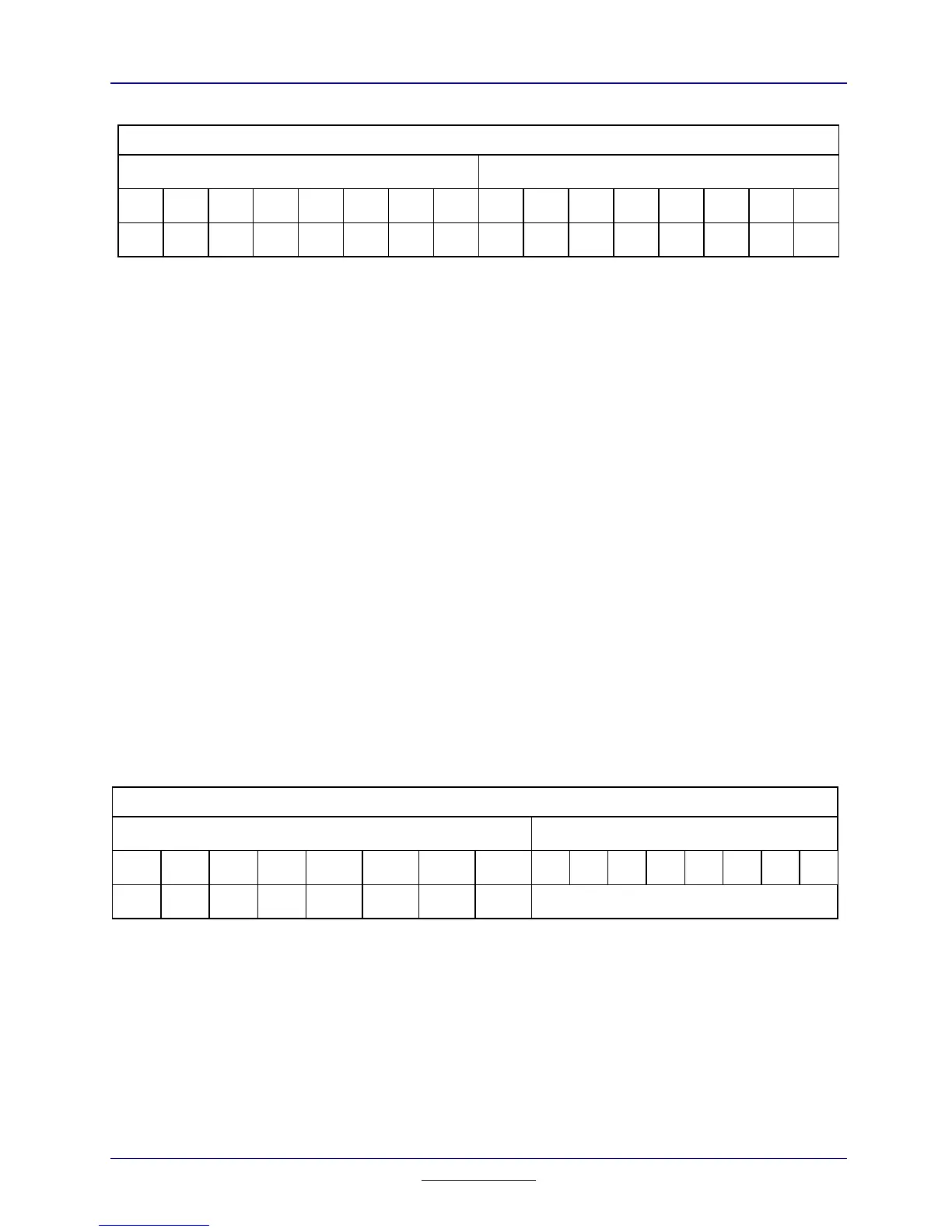

0x60000C DBus configuration / status (IE = Interrupt Enable)

Control Status

1514131211109876543210

AE LD LTO CLE CAIE CTX CRX SLE STX SRX SLI SA

Table 3.5: DBus Configuration Register

AE Autostart enable

LD Link disable

LTO Link time-out disable

CLE Control Link error IE

CAIE Control Autostart IE

CTX Control TX buffer empty IE

CRX Control RX buffer full IE

SLE Status Link error

STX Status TX buffer empty

SRX Status RX buffer full

SLI Status Link interrupt

SA Status Autostart

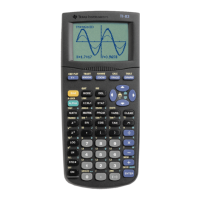

DBus is a three line serial IO interface; D0, D1 and ground. The following two

registers are used to send and receive data through the DBus port. Reading the

DBus status register resets that register.

0x60000E Link Data — Send / receive data through the link port.

Low High

1514 13 12 11 10 9 8 76543210

D1 In D0 In D1 Out D0 Out RX / TX buffer

Table 3.6: Link Register

Autostart works in conjunction with the sleep/wake up register. If this bit is set

and bit three of the sleep/wake-up register is set, the system will wake on DBus

activity.

Link disable can be used to allow for direct monitoring of the DBus lines (see

next register). When this bit is set, the state machine and barrel shifter that

decode the DBus protocol and perform serial to parallel conversion are disabled.

Loading...

Loading...