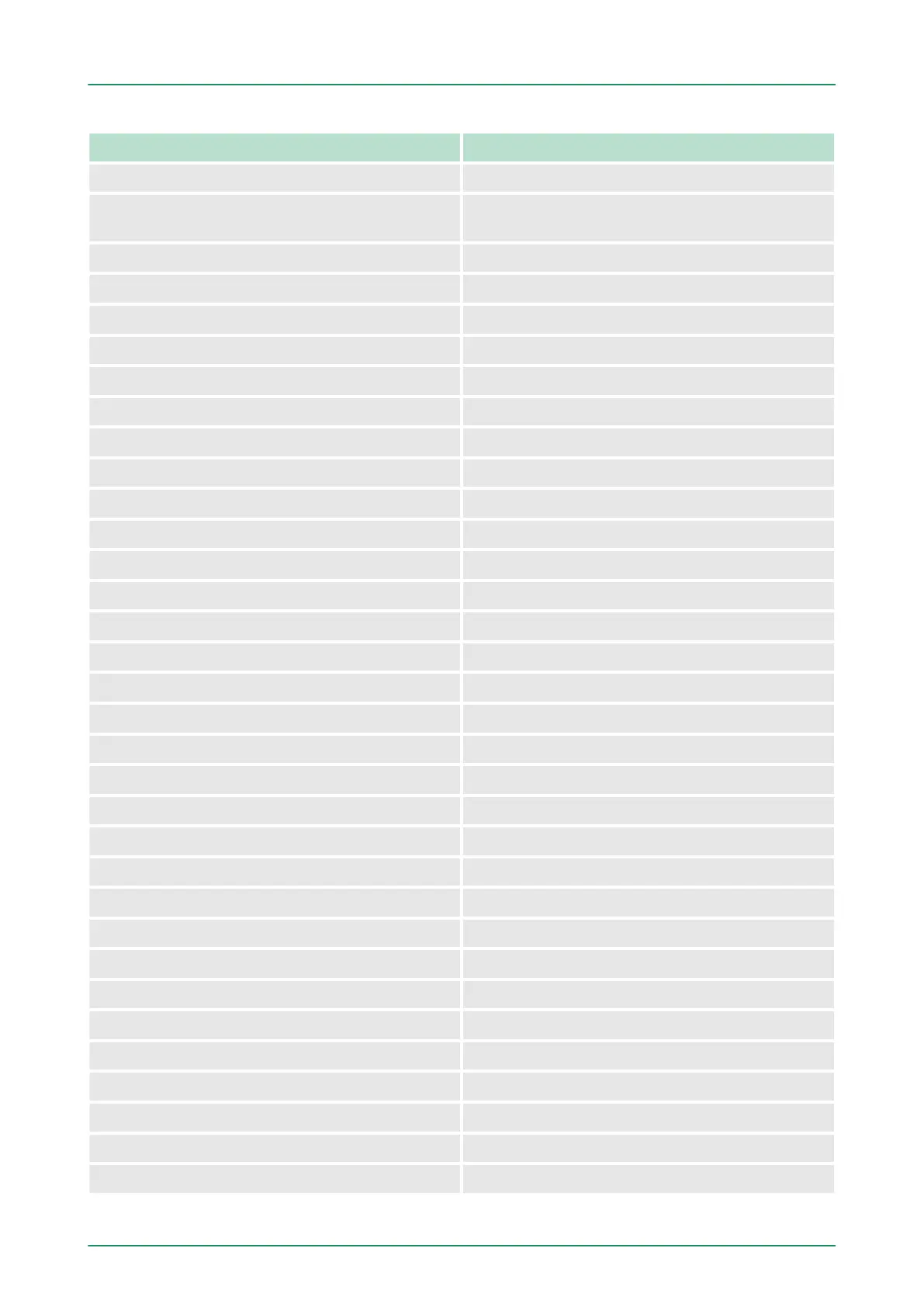

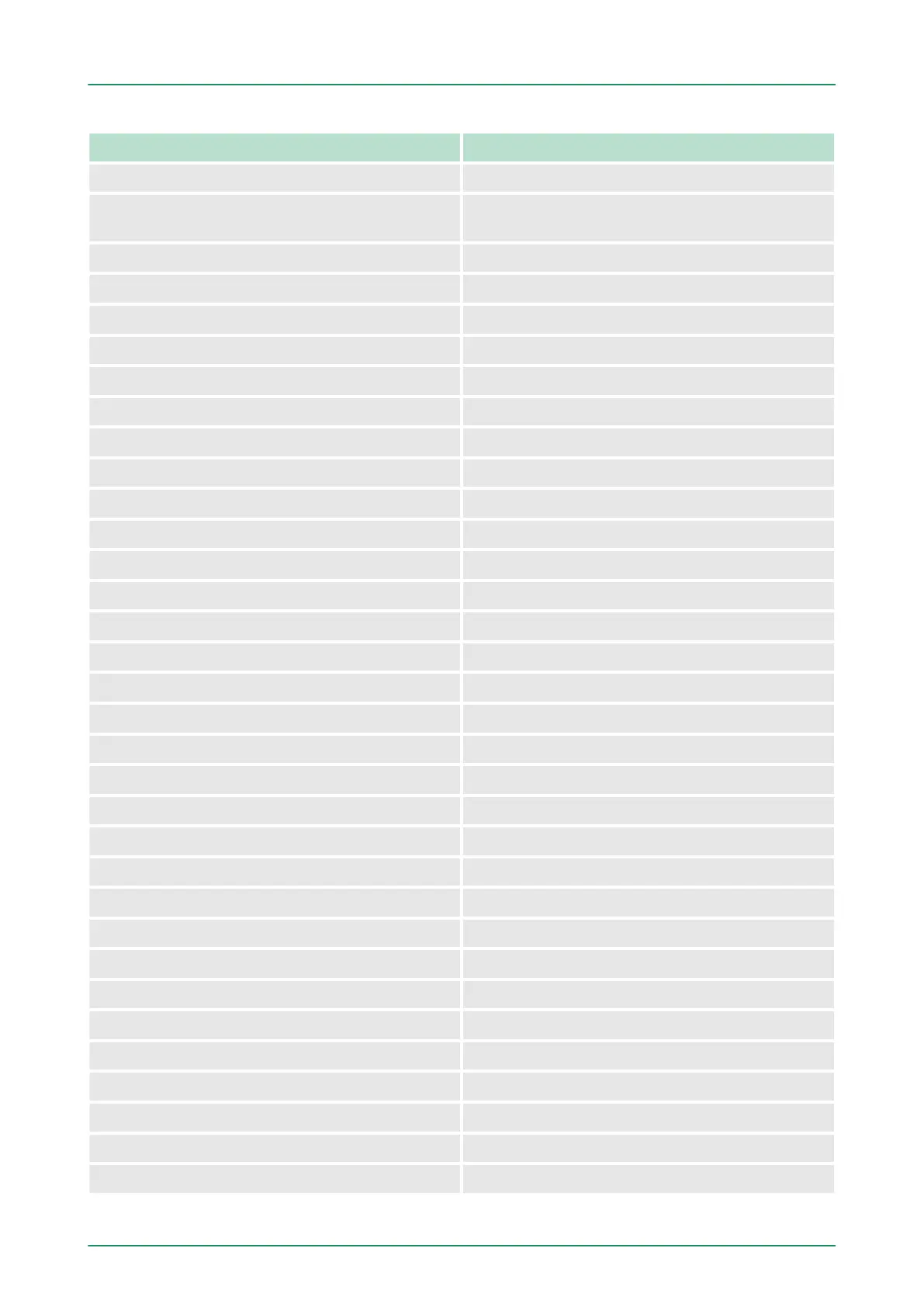

Order no. 314-6CF03

Maximum nesting depth per priority class 8

Maximum nesting depth additional within an

error OB

4

Time

Real-time clock buffered

ü

Clock buffered period (min.) 6 w

Accuracy (max. deviation per day) 10 s

Number of operating hours counter 8

Clock synchronization

ü

Synchronization via MPI Master/Slave

Synchronization via Ethernet (NTP) no

Address areas (I/O)

Input I/O address area 8192 Byte

Output I/O address area 8192 Byte

Input process image maximal 2048 Byte

Output process image maximal 2048 Byte

Digital inputs 65536

Digital outputs 65536

Digital inputs central 1032

Digital outputs central 1032

Integrated digital inputs 8

Integrated digital outputs 8

Analog inputs 1024

Analog outputs 1024

Analog inputs, central 261

Analog outputs, central 258

Integrated analog inputs 5

Integrated analog outputs 2

Communication functions

PG/OP channel

ü

Global data communication

ü

Number of GD circuits, max. 4

Size of GD packets, max. 22 Byte

S7 basic communication

ü

VIPA System 300S Hardware description

Technical data

HB140 | CPU | 314-6CF03 | GB | 16-43 49

Loading...

Loading...