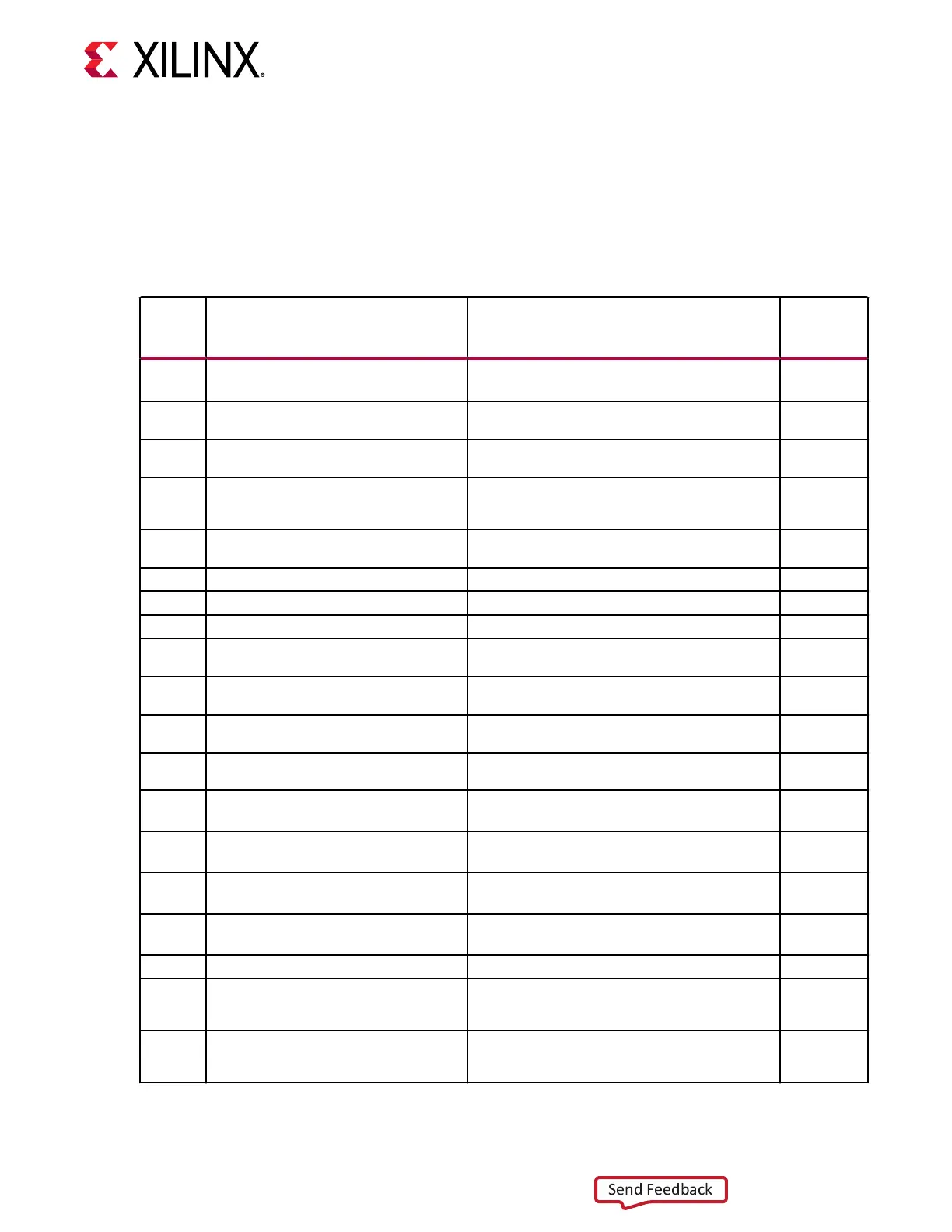

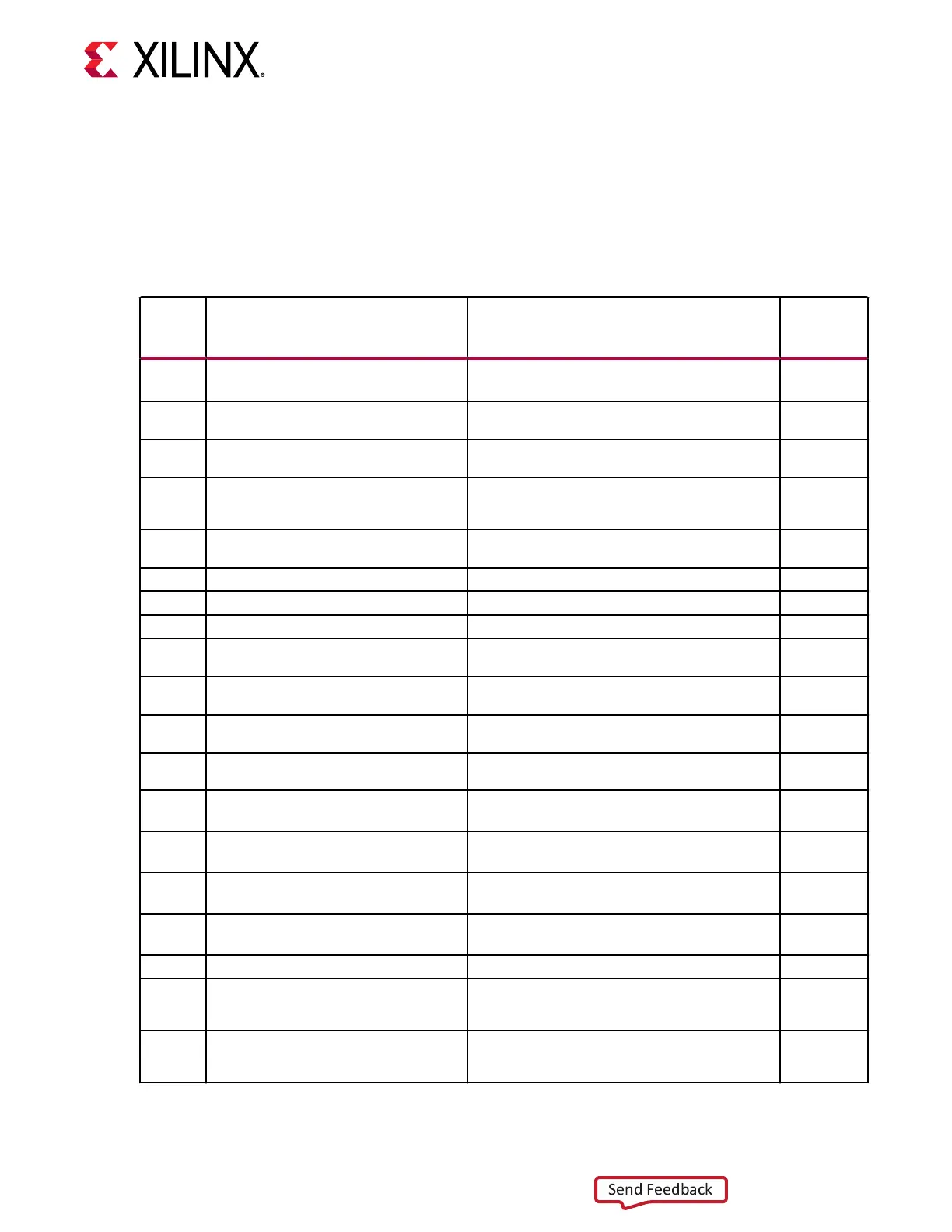

Board Component Descriptions

The following table idenes the components, references the respecve schemac page

numbers, and links to a detailed funconal descripon of the components and board features in

Chapter 3: Board Component Descripons.

Table 1: Board Component Descriptions

Callout Feature [U#] = Bottom Notes

Schematic

Page

Number

1 Virtex UltraScale+ XCVU37P-2FSVH2892E

Device (with fan-sink on soldered FPGA)

XCVU37P-2FSVH2892E

Cofan 30-4811

2 GTY transceivers, Right-side Quads (twelve

quads)

Embedded within FPGA U1 14-15

3 GTY transceivers, Left-side Quads (twelve

quads)

Embedded within FPGA U1 16-17

4 DDR4 Component Memory, 72-bit DDR4

component memory I/F, (U17-U19), [U73,

U74]

5 x Micron MT40A256M16GE-075E 24-26

5 RLD3 Component Memory, RLD3 72-bit

component memory I/F (U37, U39)

2 x Micron MT44K32M36RB-107E 29-30

6 QDR4 Component Memory (U40) Cypress CY7C4142KV13-106FCXC 27

7 Quad SPI Flash Memory (U46) Micron MT25QU02GCBB8E12-0SIT 3

8 System Controller, Zynq

®

-7000 SoC (U42) XC7Z010CLG225 48-50

9 System Controller Quad SPI Flash Memory

[U89]

Micron MT25QU02GCBB8E12-0SIT 49

10 DDR4 Component Memory I/F clock, fixed

100 MHz LVDS [U76]

SiTime SIT9120AI-2D3-33E100.0000 32

11 RLD3 Component Memory I/F clock, fixed

100 MHz LVDS (U45)

SiTime SIT9120AI-2D3-33E100.0000 32

12 QDR4 Component Memory I/F clock, fixed

100 MHz LVDS [U96]

SiTime SIT9120AI-2D3-33E100.0000 32

13 Programmable QSFP1 Clock I2C, LVDS

[U95]

Silicon Labs SI570BAB0000544DG

(default 156.250 MHz)

40

14 Programmable QSFP2 Clock I2C, LVDS

[U90]

Silicon Labs SI570BAB0000544DG

(default 156.250 MHz)

40

15 Programmable QSFP3 Clock I2C, LVDS

[U82]

Silicon Labs SI570BAB0000544DG

(default 156.250 MHz)

40

16 Programmable QSFP4 Clock I2C, LVDS

[U80]

Silicon Labs SI570BAB0000544DG

(default 156.250 MHz)

40

17 QSFP Jitter Attenuated Clock, [U87] Silicon Labs SI5328B-C-GMR 40

18 User QSFP SMA Clock pair J24(P)/J26(N)

input to XCVU37P U1 GTY131

MGTREFCLK1P/N

Rosenberger 32K10K-400L5 12

19 Four 28 Gb/s zQSFP+ Module Connectors,

QSFP1-4 (J42), (J39), (J35), (J32) + 1x4

ganged cage

4 x TE 1551920-2 connectors with TE 2170745-2

cage with heatsink

38, 39

Chapter 2: Board Setup and Configuration

UG1302 (v1.0) December 21, 2018 www.xilinx.com

VCU128 Board User Guide 11

Loading...

Loading...