ZC702 Board User Guide www.xilinx.com 33

UG850 (v1.7) March 27, 2019

Feature Descriptions

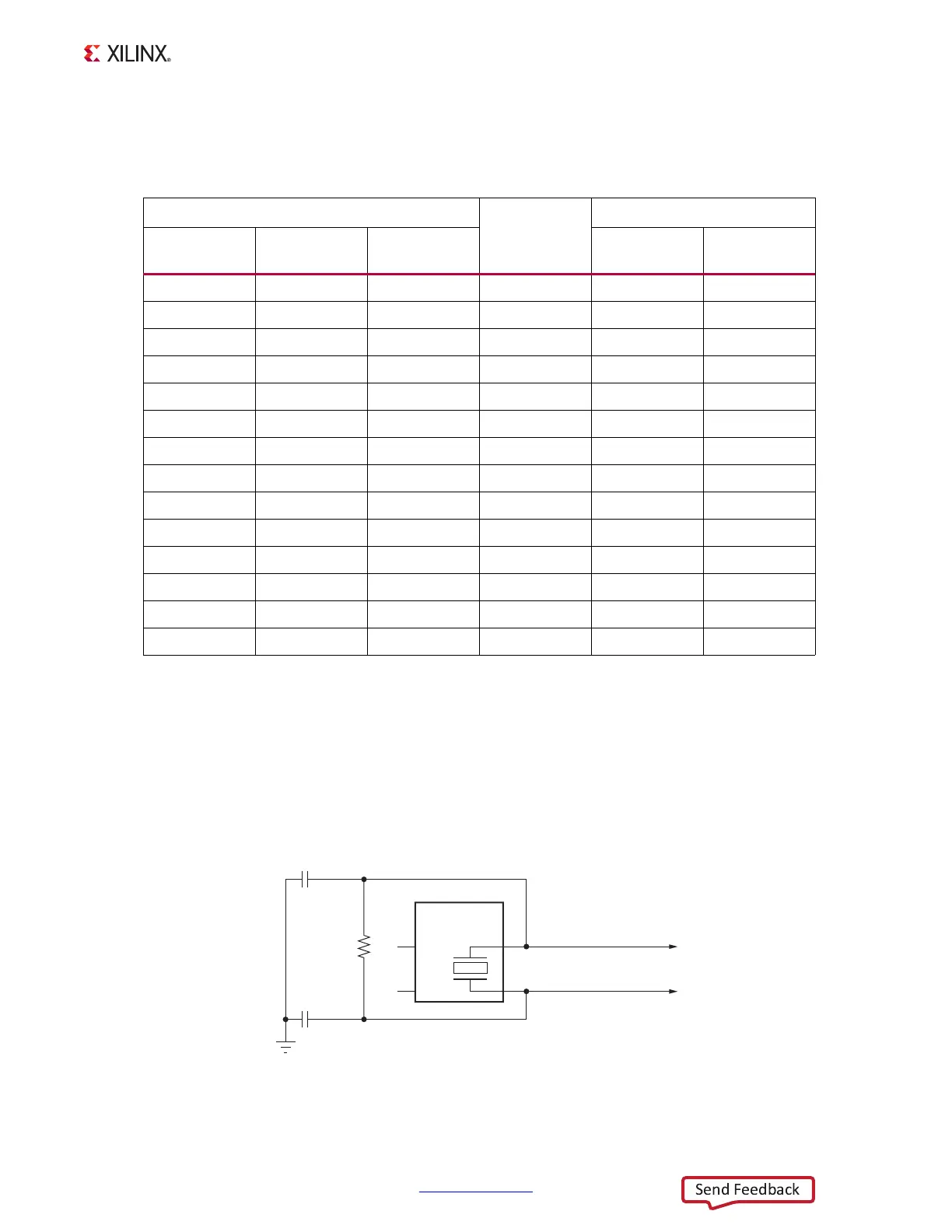

The Ethernet connections from the XC7Z020 SoC at U1 to the 88E1116R PHY device at U35

are listed in Table 1-14.

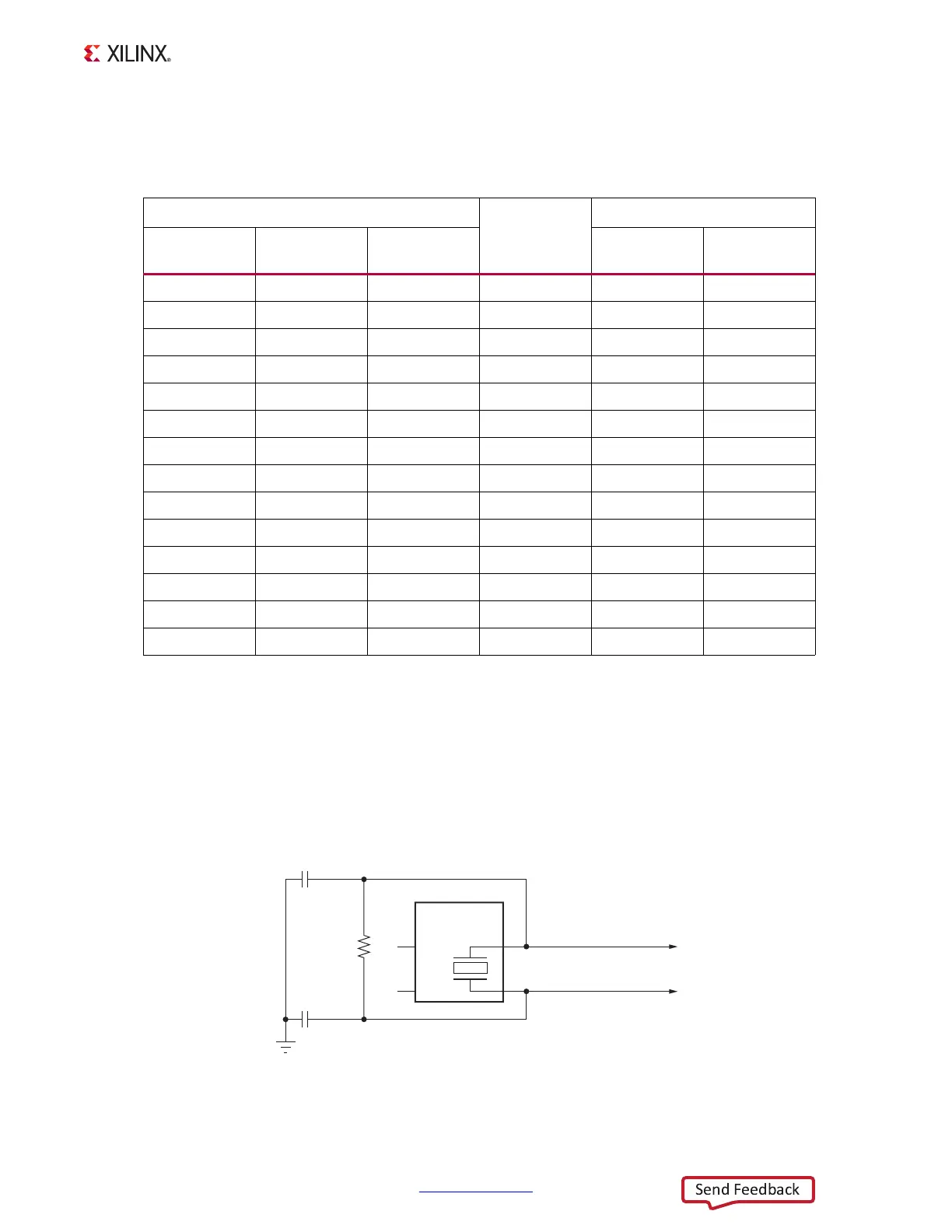

Ethernet PHY Clock Source

[Figure 1-2, callout 10]

A 25.00 MHz 50 ppm crystal at X1 is the clock source for the 88E1116R PHY at U35.

Figure 1-14 shows the clock source.

Table 1-14: Ethernet Connections, XC7Z020 SoC to the PHY Device

XC7Z020 (U1) Pin

Schematic

Net Name

M88E1116R PHY U35

Pin Name Bank

Pin

Number

Pin Name

PS_MIO53 501 C12 PHY_MDIO 45 MDIO

PS_MIO52 501 D10 PHY_MDC 48 MDC

PS_MIO16 501 D6 PHY_TX_CLK 60 TX_CLK

PS_MIO21 501 F11 PHY_TX_CTRL 63 TX_CTRL

PS_MIO20 501 A8 PHY_TXD3 62 TXD3

PS_MIO19 501 E10 PHY_TXD2 61 TXD2

PS_MIO18 501 A7 PHY_TXD1 59 TXD1

PS_MIO17 501 E9 PHY_TXD0 58 TXD0

PS_MIO22 501 A14 PHY_RX_CLK 53 RX_CLK

PS_MIO27 501 D7 PHY_RX_CTRL 49 RX_CTRL

PS_MIO26 501 A13 PHY_RXD3 55 RXD3

PS_MIO25 501 F12 PHY_RXD2 54 RXD2

PS_MIO24 501 B7 PHY_RXD1 51 RXD1

PS_MIO23 501 E11 PHY_RXD0 50 RXD0

X-Ref Target - Figure 1-14

Figure 1-14: Ethernet PHY Clock Source

UG850_c1_14_030513

GND

R246

DNP

C322

18pF 50V

NPO

C333

18pF 50V

NPO

PHY XTAL OUT

X1

25.00 MHz

PHY XTAL IN

3

4

1

2

Loading...

Loading...