ZC702 Board User Guide www.xilinx.com 54

UG850 (v1.7) March 27, 2019

Feature Descriptions

FPGA Mezzanine (FMC) Card Interface

[Figure 1-2, callout 24]

The ZC702 board supports the VITA 57.1 FPGA Mezzanine Card (FMC) specification [Ref 6]

by providing subset implementations of low pin count (LPC) connectors at J3 and J4. Both

connectors use a 10 x 40 form factor that is partially populated with 160 pins. The

connectors are keyed so that a the mezzanine card faces away from the ZC702 board when

connected.

Connector Type:

• Samtec SEAF series, 1.27 mm (0.050 in) pitch. Mates with SEAM series connector.

For more information about SEAF series connectors, go to the Samtec website [Ref 28].

LPC Connectors J3 and J4

[Figure 1-2, callout 24]

The 160-pin FMC LPC connector is shown in Figure B-1.

The LPC connections between FMC1 (J3) and XC7Z020 SoC U1 (Table 1-28) and between

FMC2 (J4) and XC7Z020 SoC U1 (Table 1-29) both implement a subset of this connectivity

(GTX is not supported):

• 68 single-ended or 34 differential user-defined signals (34 LA pairs, LA00–LA33)

•0 GTX transceivers

•0 GTX clocks

• 2 differential clocks

• 61 ground and 9 power connections

Note:

FMC1 (J3) and FMC2 (J4) GA0 = GA1 = 0 (GND).

Table 1-28 shows the LPC connections between J3 and XC7Z020 SoC U1.

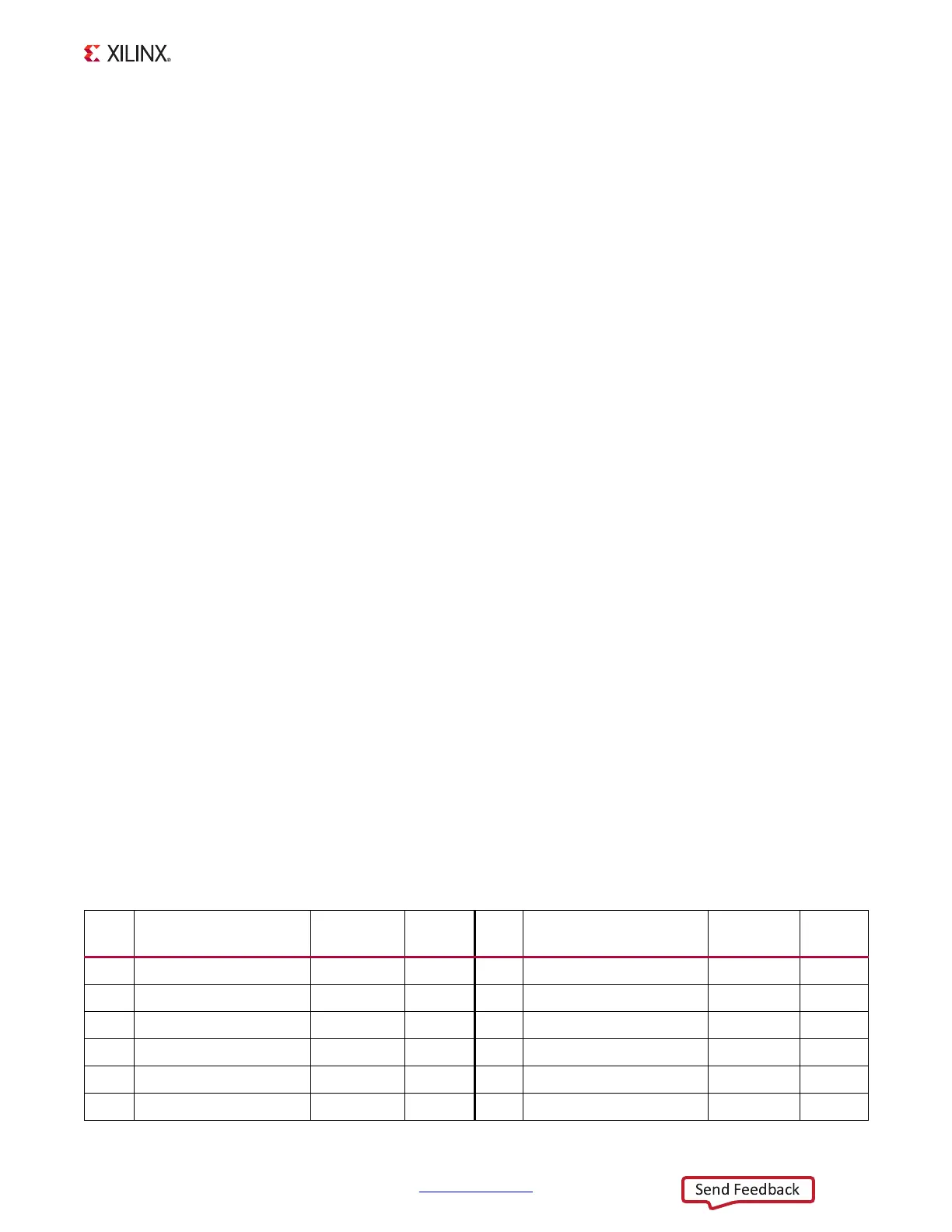

Table 1-28: LPC Connections, FMC1 (J3) to XC7Z020 SoC U1

FMC1

J3 Pin

Net Name

I/O

Standard

XC7Z020

(U1) Pin

FMC1

J3 Pin

Net Name

I/O

Standard

XC7Z020

(U1) Pin

C2 NC D1 PWRCTL2_VCC4A_PG

C3 NC D4 NC

C6 NC D5 NC

C7 NC D8 FMC1_LPC_LA01_CC_P LVCMOS25 N19

C10 FMC1_LPC_LA06_P LVCMOS25 J18 D9 FMC1_LPC_LA01_CC_N LVCMOS25 N20

C11 FMC1_LPC_LA06_N LVCMOS25 K18 D11 FMC1_LPC_LA05_P LVCMOS25 N17

Loading...

Loading...