6-5

IM 710105-17E

Status Reports

6

6.4 Extended Event Register

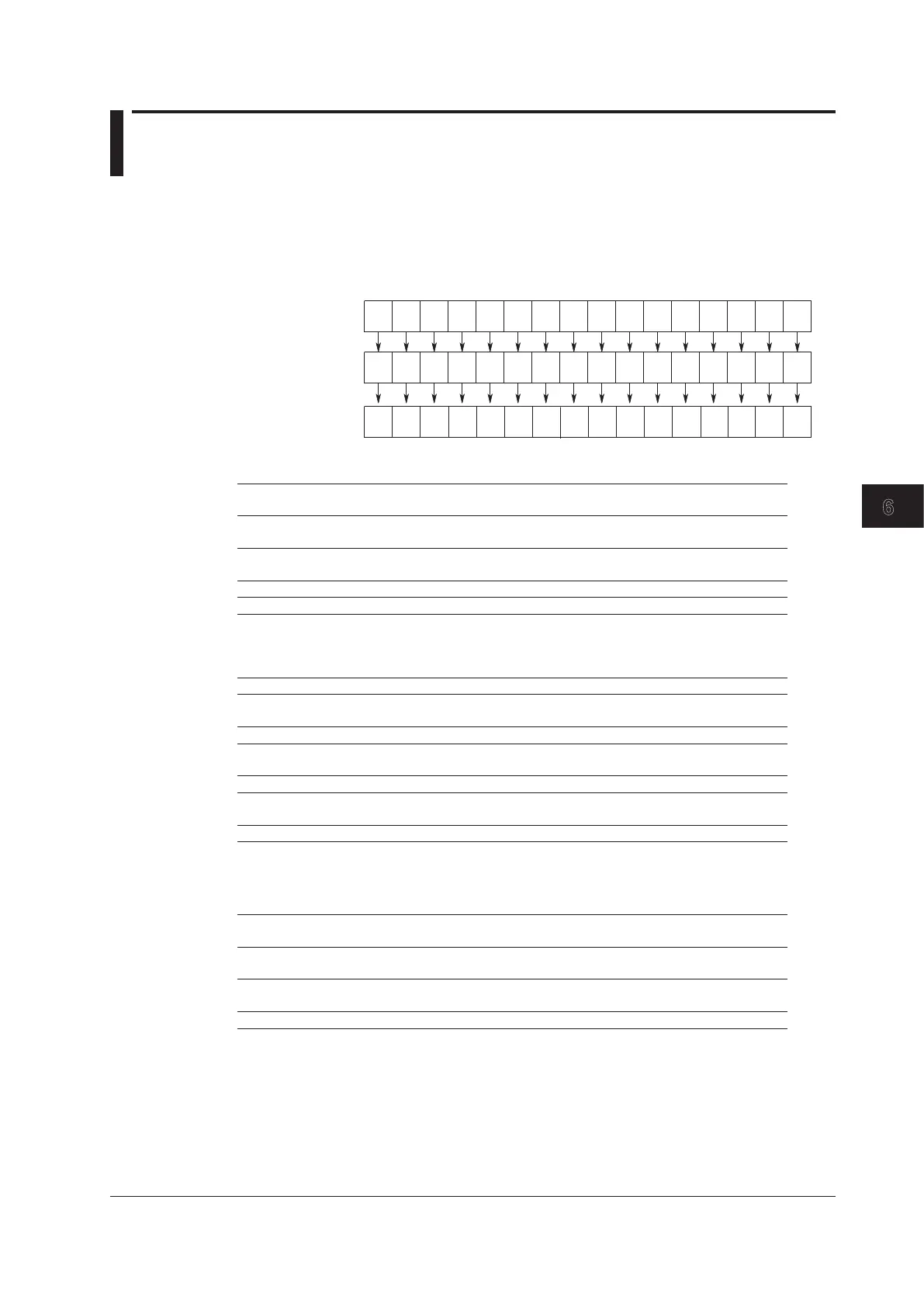

The extended event register receives information about changes in the condition register, which

indicates the DLM2000’s internal condition. The information is the result of edge detection

performed by the transition filter.

ACS

6

HST

7 5 4 3 2 1 0

PRN TST CAL TRG CUR RUN NGO SCH

8

0

9

MES

10 11

NSG

12

0

13

AN

14

0

15

6 7 5 4 3 2 1 0 8 9 10 11 12 13 14 15

Condition register

:STATus:CONDition?

Transition filter

0 14 15

1

6 7 5 4 3 8 9 10 11 12 13

2

6 7 5 4 3 2 1 8 9 10 11 12 13 14 15

16

:STATus:FILTer<x>

{RISE | FALL | BOTH | NEVer}

FILTer<x>→

The condition register bits are described below.

Bit 0 RUN (Running) This bit is set to 1 when waveform acquisition is in

progress.

Bit 1 CUR (Cursor) This bit is set to 1 when cursor measurement is in

progress.

Bit 2 TRG (Awaiting trigger) This bit is set to 1 when the DLM2000 is waiting for a

trigger.

Bit 3 CAL (Calibration) This bit is set to 1 when calibration is in progress.

Bit 4 TST (Testing) This bit is set to 1 when a self-test is in progress.

Bit 5 PRN (Printing) This bit is set to 1 when the built-in printer is in operation,

when data is being transmitted to an external USB or

network printer, or when screen capture data is being

saved.

Bit 6 ACS (Accessing) This bit is set to 1 when a drive is being accessed.

Bit 7 MES (Measuring) This bit is set to 1 when automated measurement of

waveform parameters is in progress.

Bit 8 HST (History Search) This bit is set to 1 when a history search is in progress.

Bit 10 NGO (Go/No-go) This bit is set to 1 when a GO/NO-GO search is in

progress.

Bit 11 SCH (Search) This bit is set to 1 when a search is in progress.

Bit 12 NSG (N-Single) This bit is set to 1 when consecutive acquisition is in

progress when the trigger mode is set to Single (N).

Bit 14 AN (Analysis) This bit is set to 1 when an analysis is in progress.

The transition filter parameters detect changes in the specified condition register bits (numeric

suffixes 1 to 16) and overwrite the extended event register in the following ways.

RISE The specified extended event register bit is set to 1 when the corresponding condition

register bit changes from 0 to 1.

FALL The specified extended event register bit is set to 1 when the corresponding condition

register bit changes from 1 to 0.

BOTH The specified extended event register bit is set to 1 when the corresponding condition

register bit changes from 0 to 1 or from 1 to 0.

NEVer Always zero.

Loading...

Loading...