9 Basic interval timer

A96G174/A96S174 has a free running 8-bit Basic Interval Timer (BIT). BIT generates the time base for

watchdog timer counting, and provides a basic interval timer interrupt (BITIFR).

BIT of A96G174/A96S174 features the followings:

During Power On, BIT gives a stable clock generation time

On exiting Stop mode, BIT gives a stable clock generation time

As a timer, BIT generates a timer interrupt.

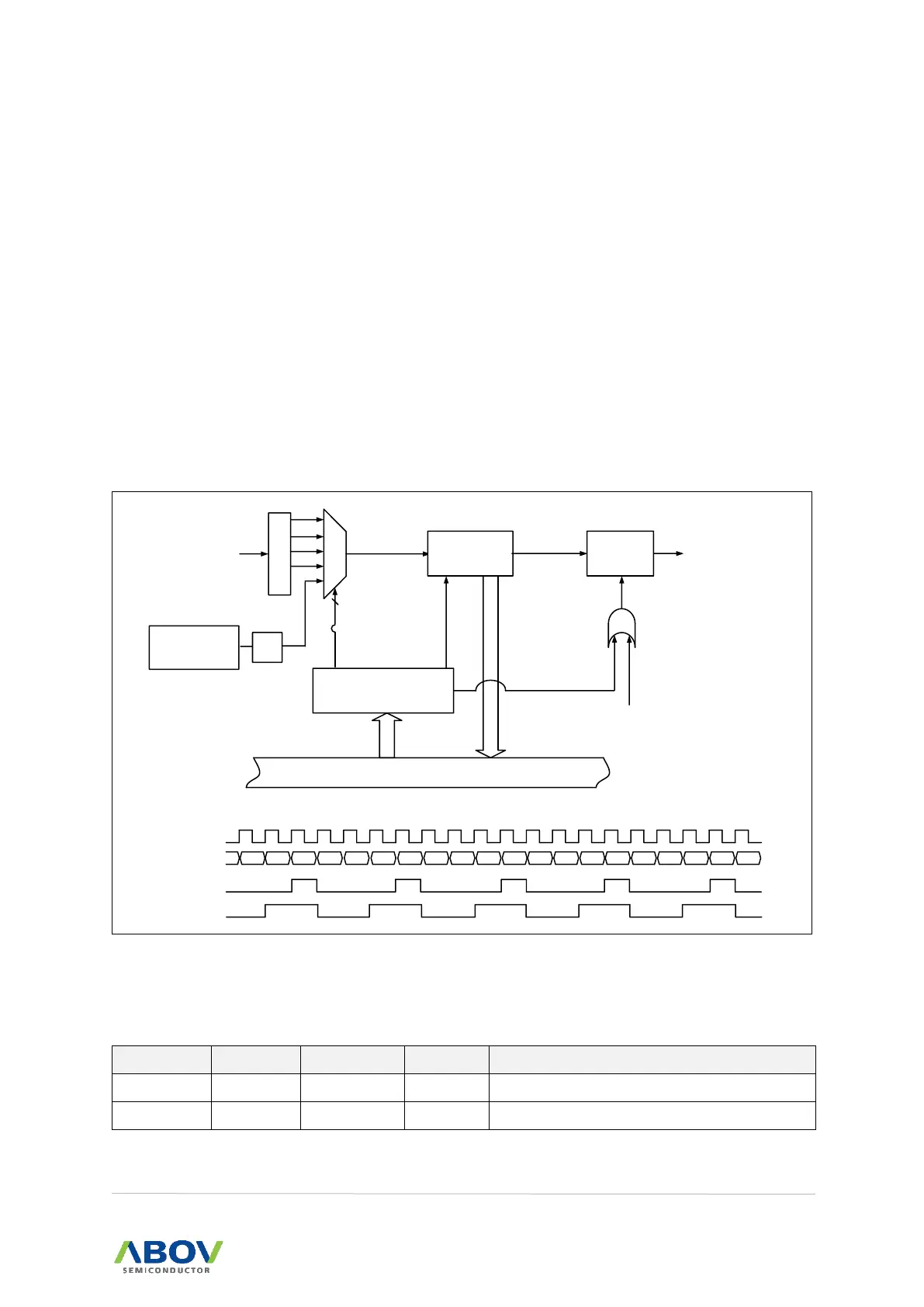

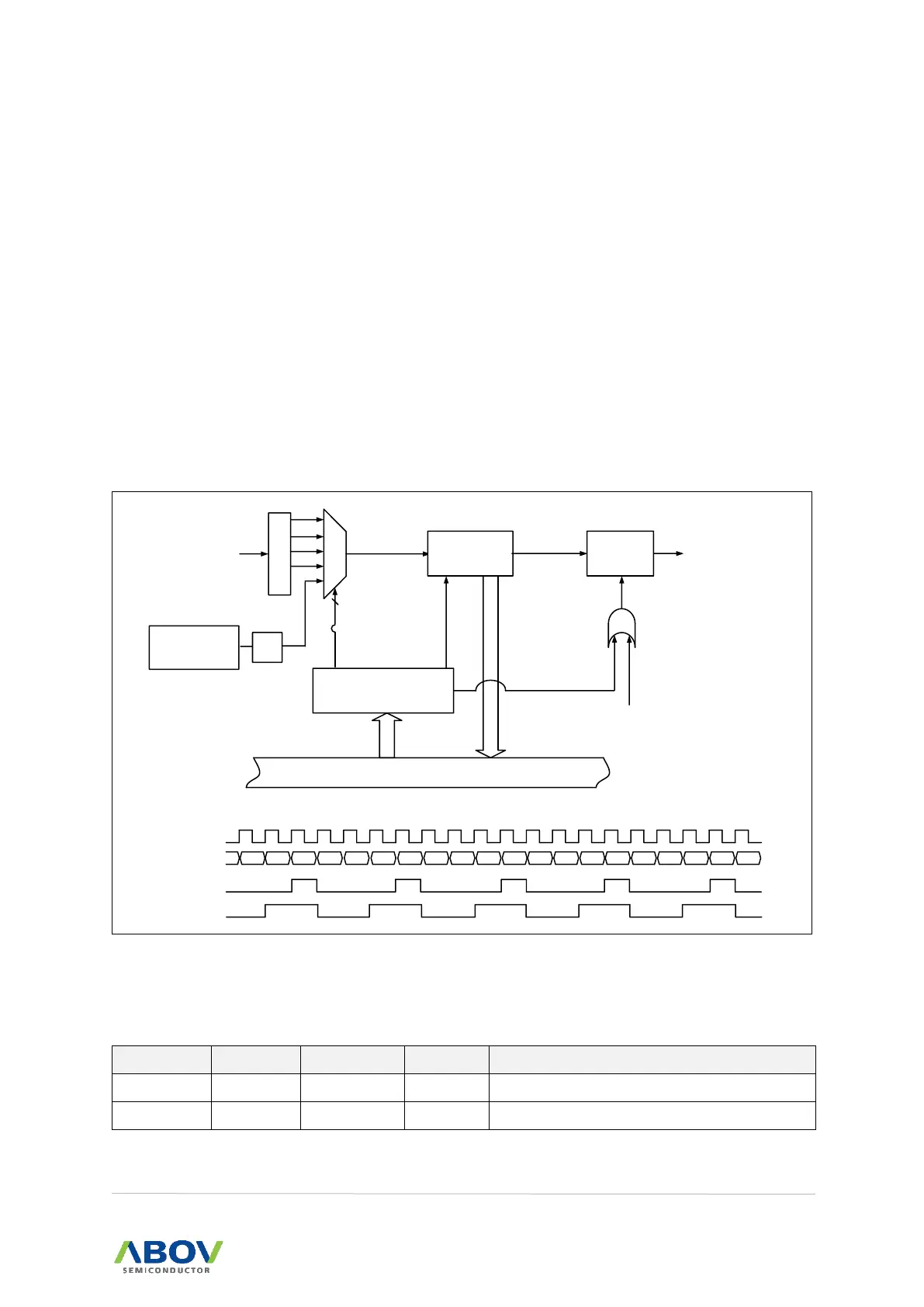

9.1 BIT block diagram

In this section, basic interval timer of A96G174/A96S174 is described in a block diagram.

Loading...

Loading...