3.3 Peripherals Connected to the FPGA

3.3.1 Communication and Configuration

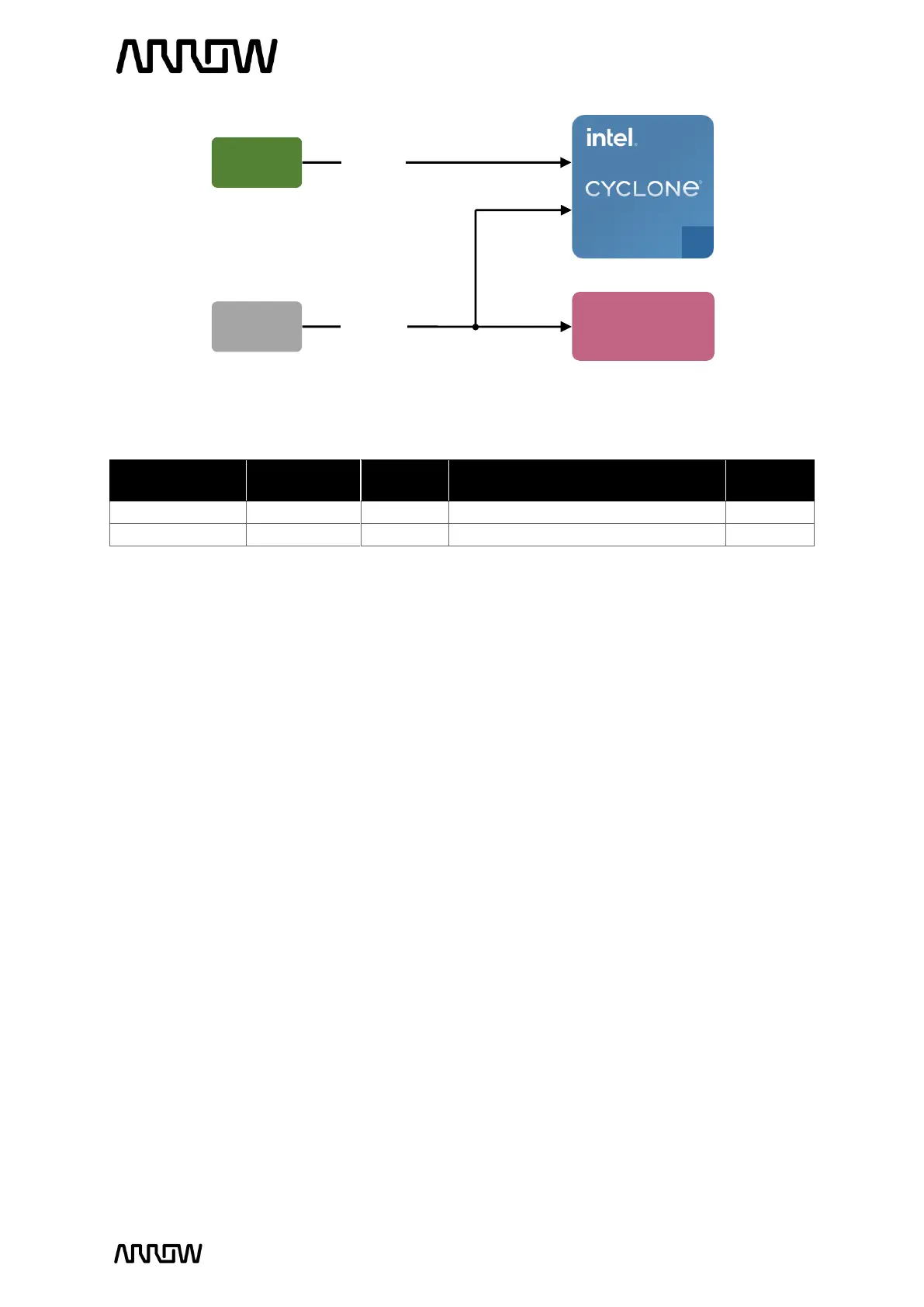

The CYC5000 board uses a single chip to perform configuration of the device and communication

over USB.

3.3.1.1 USB Communication

The FTDI chip converts signals from USB 2.0 to a variety of standard serial and parallel interfaces.

Channel A of FTDI chip is used in MPPSE mode for JTAG. Channel B is routed to FPGA and is

usable for other standard interfaces.

Loading...

Loading...