CYC5000 User Guide www.arrow.com

Page | 49 March 2023

of the counter. The signals of the counter that are not connected will not be used by

Quartus Prime.

5.2.9.10 Save your design. Open the File Menu and select “Save”. Save it as top.bdf.

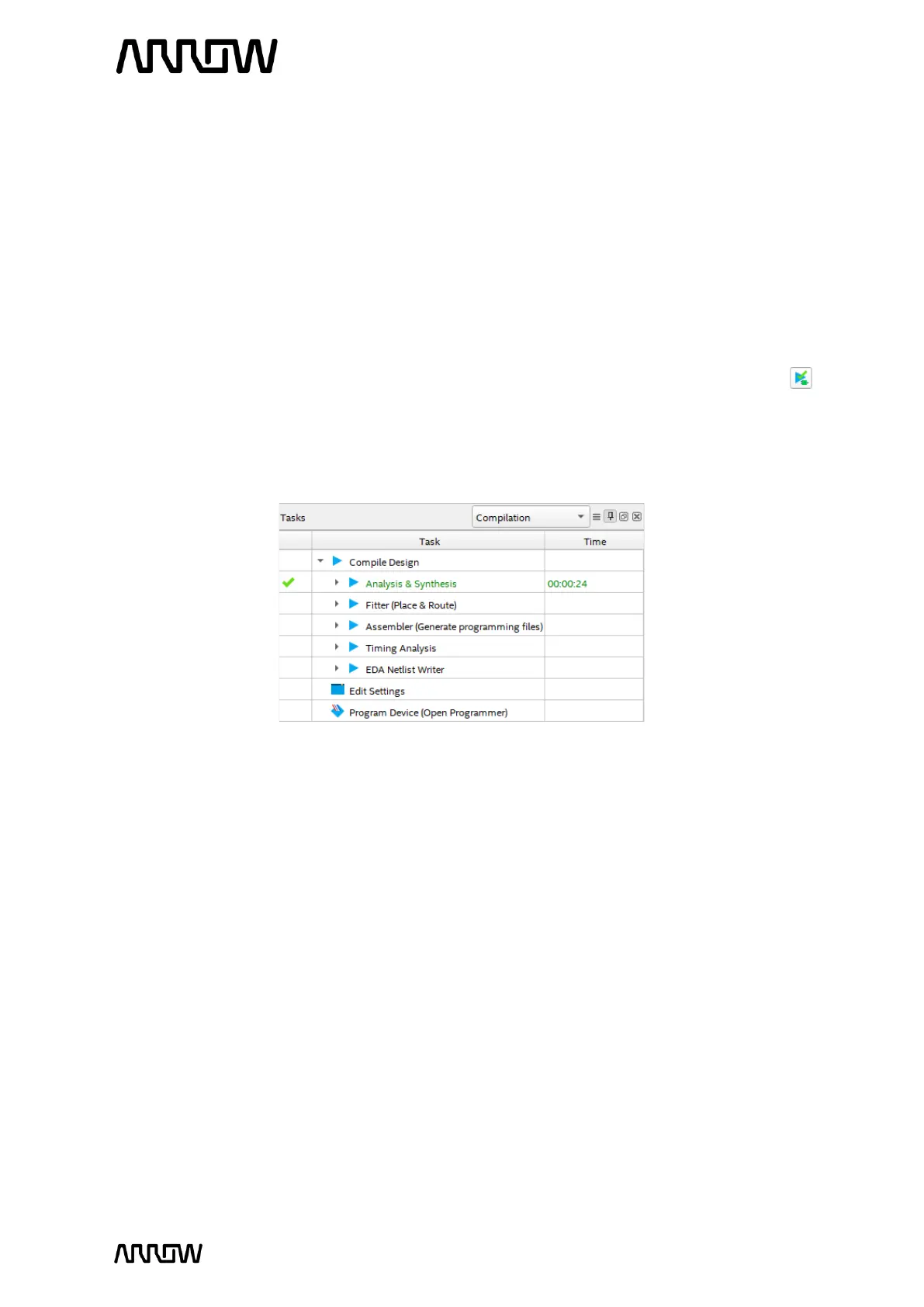

5.2.10 Analysis and Synthesis

The next step is to run Analysis and Synthesis to ensure that there are no errors in the design. To

run Analysis and synthesis open Processing → Start → Analysis and Synthesis or clicking

button on the top toolbar.

There should be no errors. If there are errors, they should be fixed before continuing and Analysis

and Synthesis run again.

5.2.11 Adding Timing Constraints

Timing Constraints tell the Quartus what the timing requirements for this design are. Timing

Constraints are required in every CPLD/FPGA design.

5.2.11.1 To add the timing constraints, select File → New and under the “Other File” section,

select “Synopsys Design Constraints File” and select “OK”.

Loading...

Loading...