CYC5000 User Guide www.arrow.com

Page | 13 March 2023

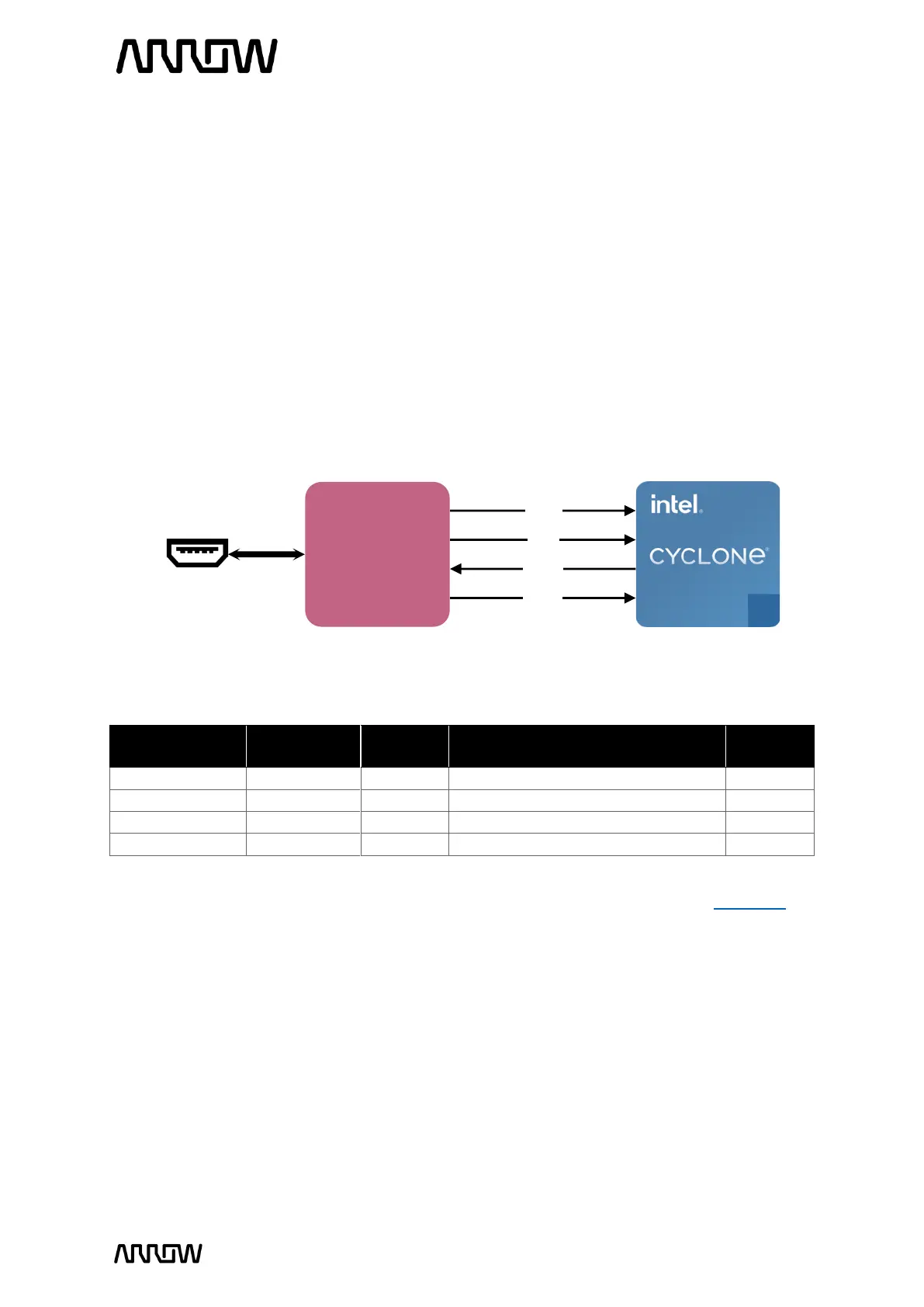

3.3.1.2 JTAG Chain Configuration

There are two types of configuration methods supported by CYC5000:

1. JTAG Configuration: configuration using JTAG ports. JTAG configuration scheme allows you

to directly configure the device core through JTAG pins (TDI, TDO, TMS and TCK pins). The

Quartus Prime software automatically generates a .sof that can be downloaded to the

Cyclone V with a download cable through the Quartus Prime Programmer. This function is

only available via the On-board Arrow USB Programmer2.

2. Configuration from QSPI flash: configuration using external flash. Before configuration, you

need to program the configuration data .jic into the configuration flash memory which

provides non-volatile storage for the bit stream. The information is retained within flash

memory even if the CYC5000 is turned off. When the board is powered on, the configuration

data in the flash memory is automatically loaded into the Cyclone V FPGA.

For detailed information about how to configure the Cyclone V, please refer to Chapter 6.

3.3.2 QSPI Configuration Flash Memory

The CYC5000 board is integrated with a 64MBit of QSPI flash memory that can be used for user

data and programming non-volatile storage. The configuration bitstream is downloaded into the

configuration device which automatically loads the configuration data into the Cyclone V when

the board is powered on. Device memory capacity not consumed storing configuration data can

be used as general-purpose non-volatile memory, which with its operation of up to 133MHz is

perfect for program and data storage. Several interfaces available with Nios II embedded

Loading...

Loading...