CYC5000 User Guide www.arrow.com

Page | 19 March 2023

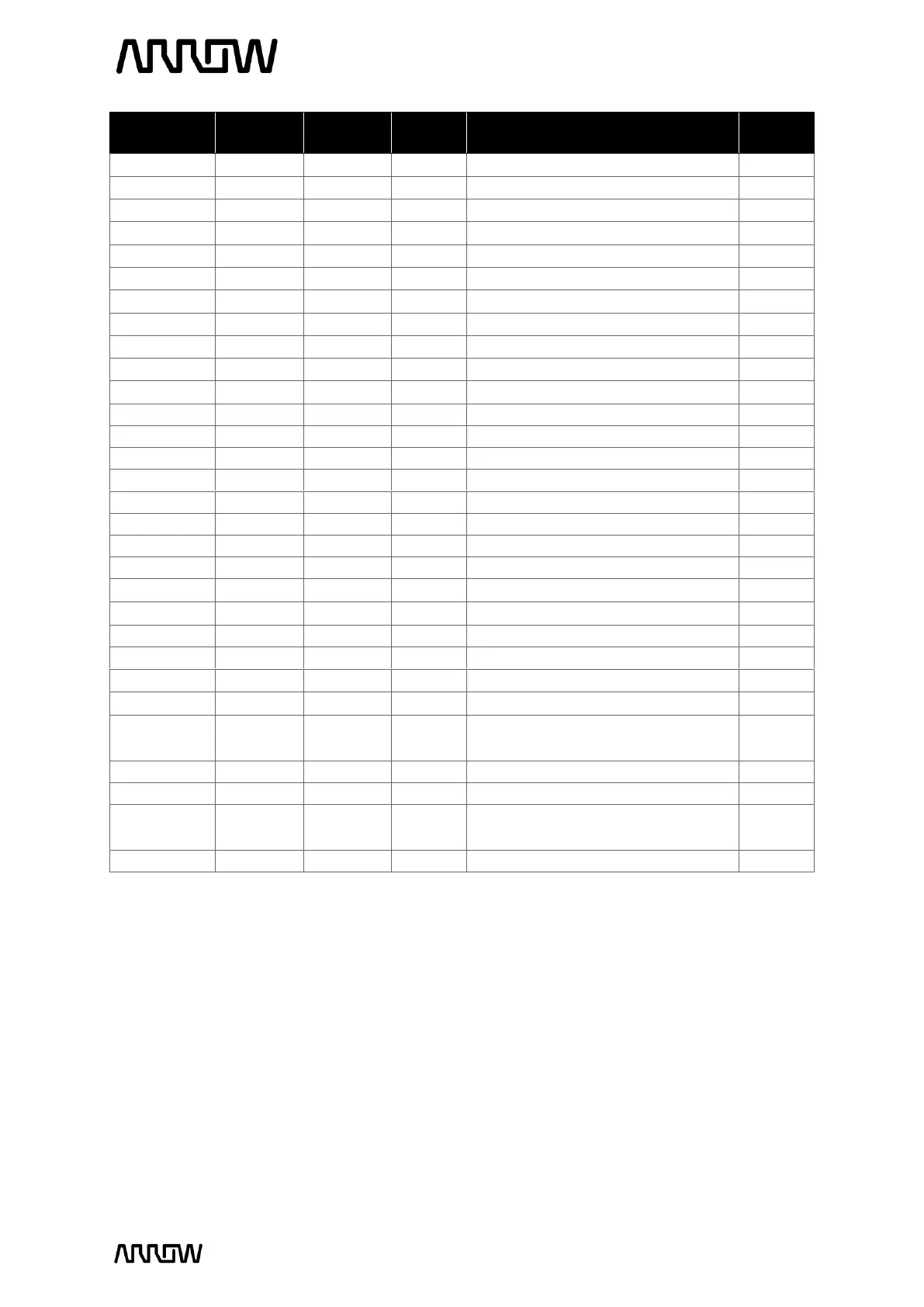

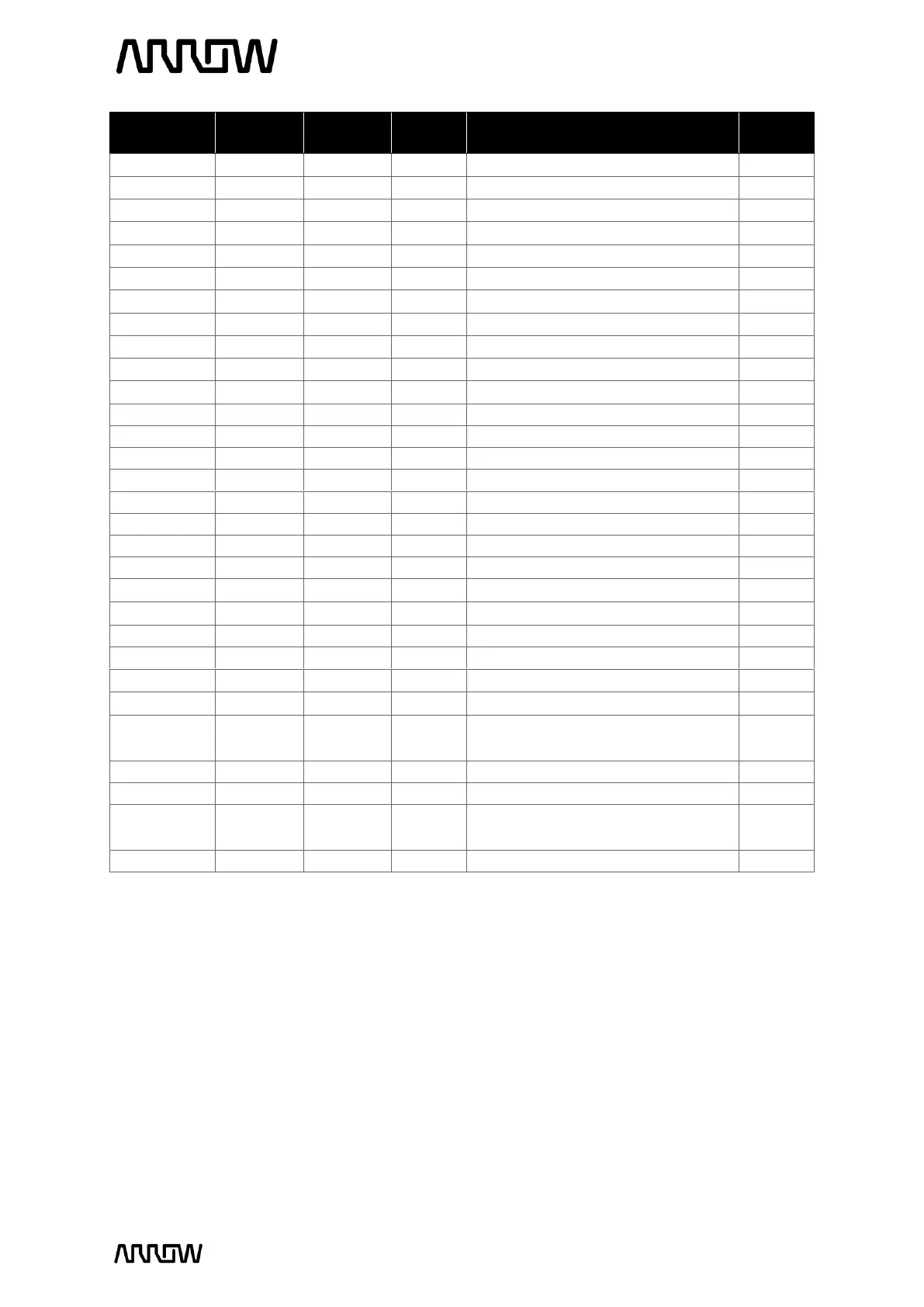

Input reference voltage or GPIO

Digital I/O [11] with resistor*

Digital I/O [12] with resistor*

System reset of the board,

controlled by the S1 user button

3.3V power to the connector

User power into to the

CYC5000 Board

5V power to the connector

*Can only choose one, hence same name pinning

3.3.6 LEDs

There are eight red user-controllable LEDs connected to the FPGA. Each LED is driven directly

and individually by the Cyclone V FPGA, driving its associated pin to a high logic level for on or

low logic level for off.

Loading...

Loading...