82

8126F–AVR–05/12

ATtiny13A

14. Analog to Digital Converter

14.1 Features

• 10-bit Resolution

• 0.5 LSB Integral Non-linearity

• ± 2 LSB Absolute Accuracy

• 13 - 260 µs Conversion Time

• Up to 15 kSPS at Maximum Resolution

• Four Multiplexed Single Ended Input Channels

• Optional Left Adjustment for ADC Result Readout

• 0 - V

CC

ADC Input Voltage Range

• Selectable 1.1V ADC Reference Voltage

• Free Running or Single Conversion Mode

• ADC Start Conversion by Auto Triggering on Interrupt Sources

• Interrupt on ADC Conversion Complete

• Sleep Mode Noise Canceler

14.2 Overview

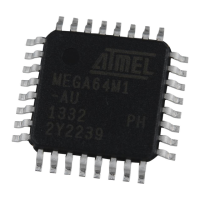

The ATtiny13A features a 10-bit successive approximation ADC. A block diagram of the ADC is

shown in Figure 14-1.

Figure 14-1. Analog to Digital Converter Block Schematic

ADC CONVERSION

COMPLETE IRQ

8-BIT DATA BUS

15 0

ADC MULTIPLEXER

SELECT (ADMUX)

ADC CTRL. & STATUS

REGISTER (ADCSRA)

ADC DATA REGISTER

(ADCH/ADCL)

ADIE

ADATE

ADSC

ADEN

ADIF

ADIF

MUX1

MUX0

ADPS0

ADPS1

ADPS2

CONVERSION LOGIC

10-BIT DAC

+

-

SAMPLE & HOLD

COMPARATOR

INTERNAL 1.1V

REFERENCE

MUX DECODER

V

CC

ADC3

ADC2

ADC1

ADC0

REFS1

ADLAR

CHANNEL SELECTION

ADC[9:0]

ADC MULTIPLEXER

OUTPUT

PRESCALER

INPUT

MUX

TRIGGER

SELECT

ADTS[2:0]

INTERRUPT

FLAGS

START

Loading...

Loading...