8062A

Instruction Manual

3-6

Read

2V dc

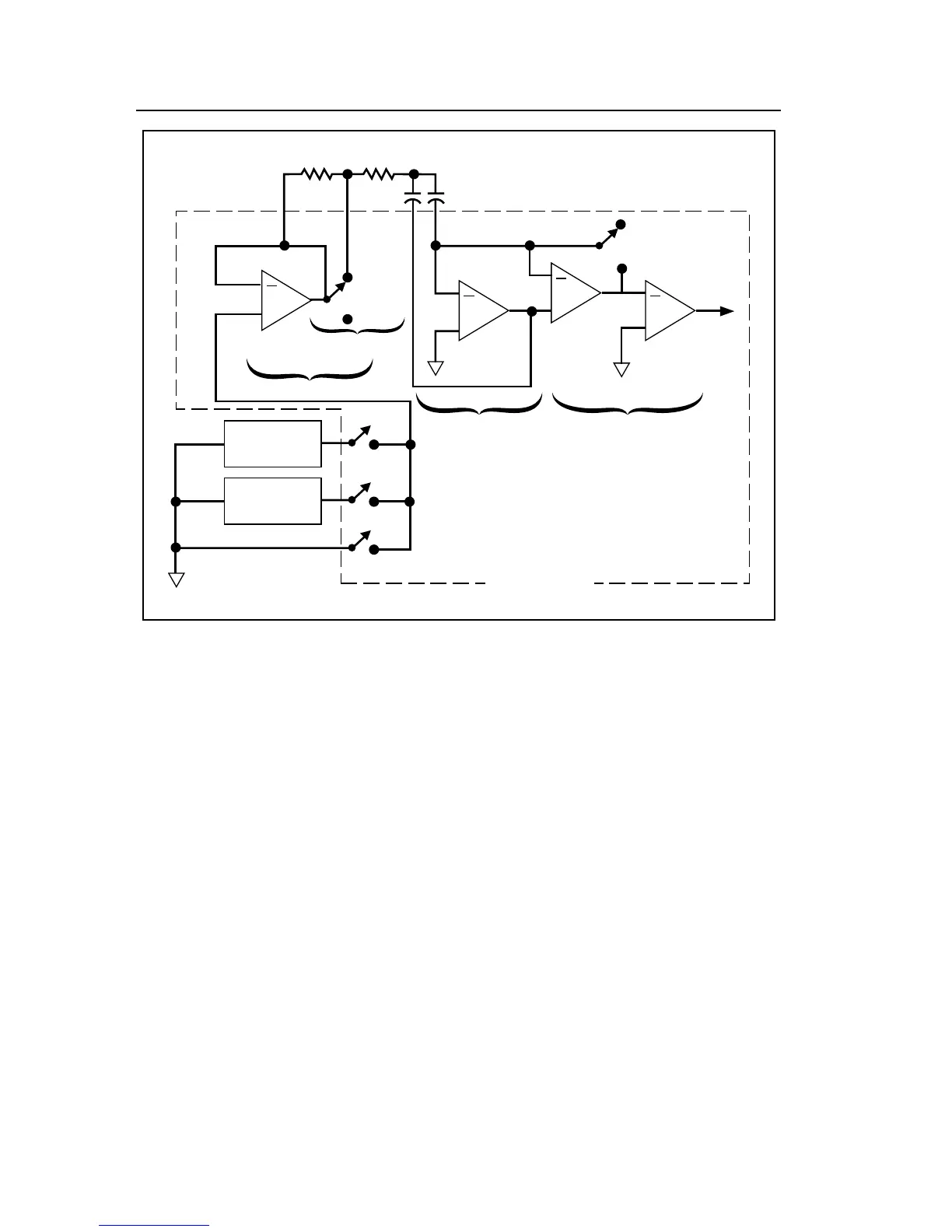

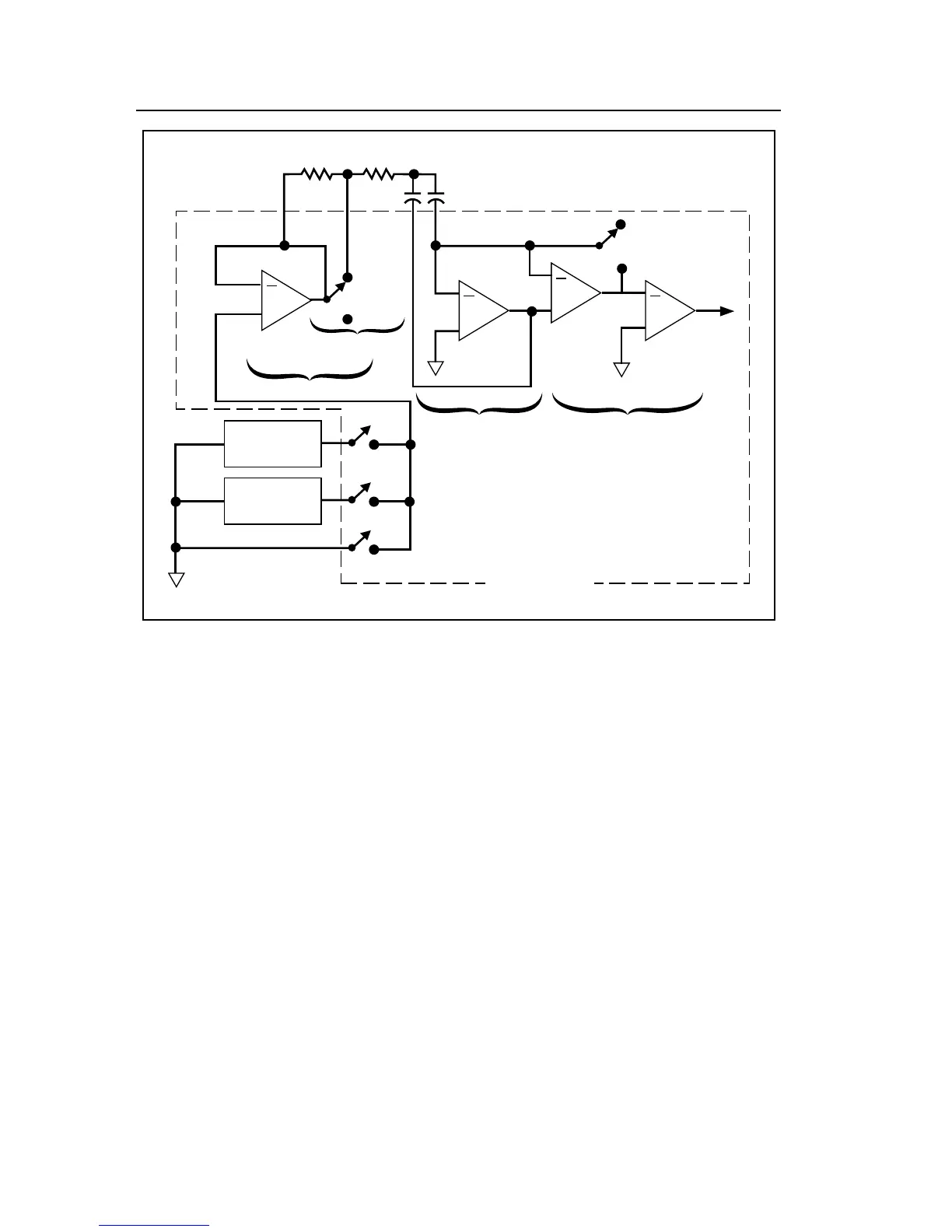

9R R

C

AZ

C

Integ

200 mV

dc

Integ

AZ

+

+

+

+

Reference

Voltage

Integrator Gain

Integrator Comparators

AZ

Integ or Read

To Digital

Control Logic

Buffer Amp

± Unkown

Input Voltage

Internal to the MAC

dy26f.eps

Figure 3-2. Analog Portion of the A/D Converter

The measurement cycle begins with the autozero period. The AZ switches

close, applying a ground reference as the input to the converter. Under ideal

conditions the output of the comparator would also go to zero. However,

input-offset voltage errors accumulate in the buffer amplifier loop, and

appear at the comparator output as an error voltage. To compensate for this

error, the error is impressed across the AZ capacitor where it is stored for the

remainder of the measurement cycle. The stored level is used to provide

offset voltage correction during the integrate and read periods.

The integrate period begins at the end of the autozero period. As the period

begins, the AZ switches open and the INTEG switches close. This applies

the unknown input voltage to the input of the converter. The voltage is

buffered and then begins charging the INTEG capacitor. The waveform at

the INTEG capacitor is a ramp from near zero to some maximum value

determined by the amplitude and polarity of the unknown input voltage.

Loading...

Loading...