7: D

EVICE

A

DDRESSES

7-4 S

MART

AXIS P

RO

/L

ITE

U

SER

'

S

M

ANUAL

FT9Y-B1378

*1 Read only when FBD program is selected as the programming method.

M8000 Start Control

M8000 is used to control the operation of the CPU. The CPU stops operation when M8000 is turned off while the CPU is running.

M8000 can be turned on or off using the WindLDR Online menu. When a stop or reset input is designated, M8000 must remain on

to control the CPU operation using the stop or reset input.

M8000 maintains its status when the CPU is powered down. When the data to be maintained during power failure is broken after

the CPU has been off for a period longer than the battery backup duration, the CPU restarts operation or not as selected in

Configuration > Run/Stop Control > Run/Stop Selection at Memory Backup Error. For details on SmartAXIS Pro/Lite

start control, see "Run/Stop Selection at Memory Backup Error" on page 5-5.

M8001 1-sec Clock Reset

While M8001 is on, M8121 (1-sec clock) is turned off.

M8002 All Outputs OFF

When M8002 is turned on, all outputs and remote outputs go off until M8002 is turned off. Self-maintained circuits using outputs

also go off and are not restored when M8002 is turned off.

M8003 Carry (Cy) and Borrow (Bw) [Ladder program only]

When a carry or borrow results from executing an addition or subtraction instruction, M8003 turns on. M8003 is also used for the

bit shift and rotate instructions. For the causes of carry (CY) and borrow (BW), when ladder program is selected as the

programming language, see Chapter 4 "Instructions Reference" – "Carry and Borrow" in the "SmartAXIS Ladder Programming

Manual".

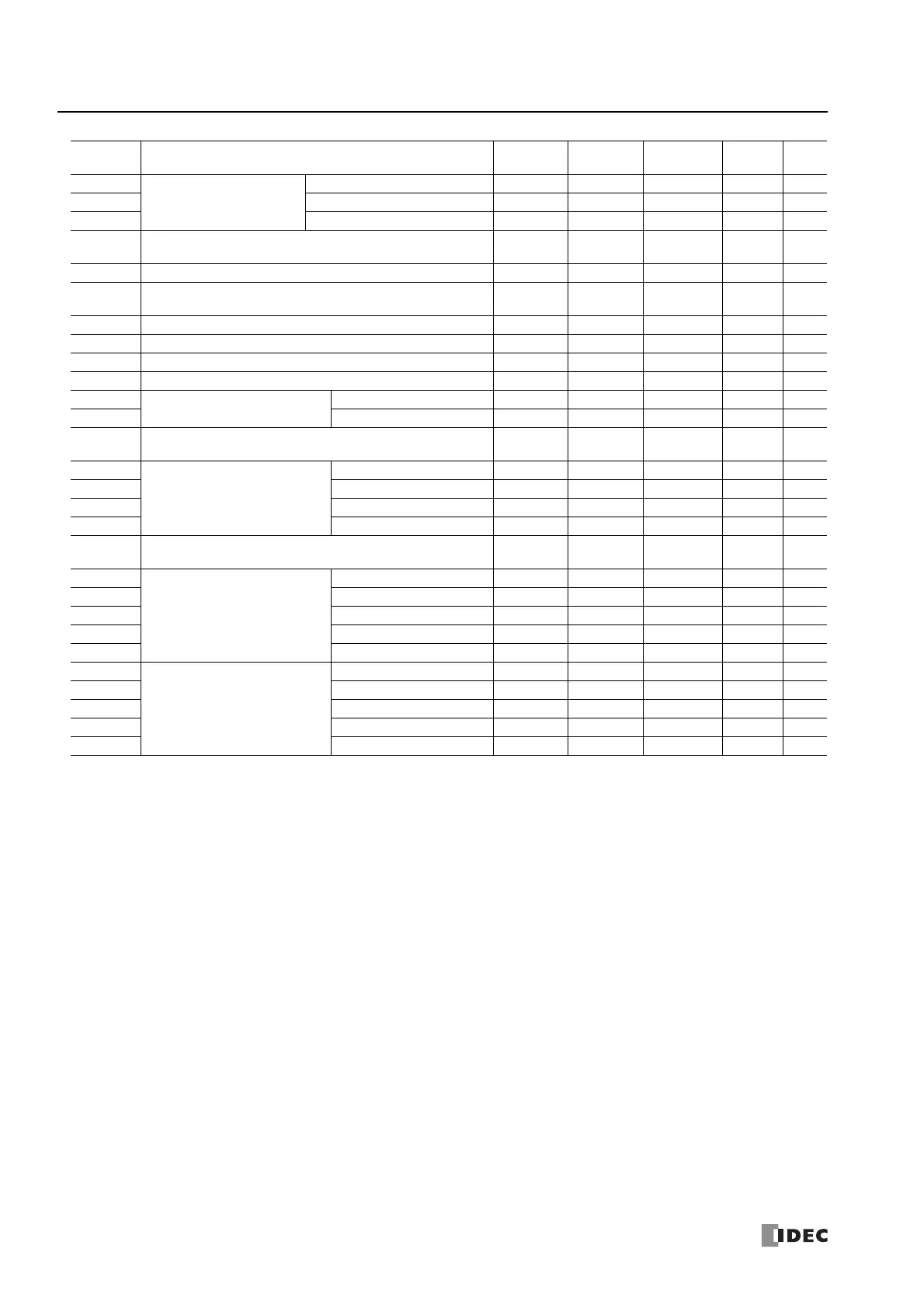

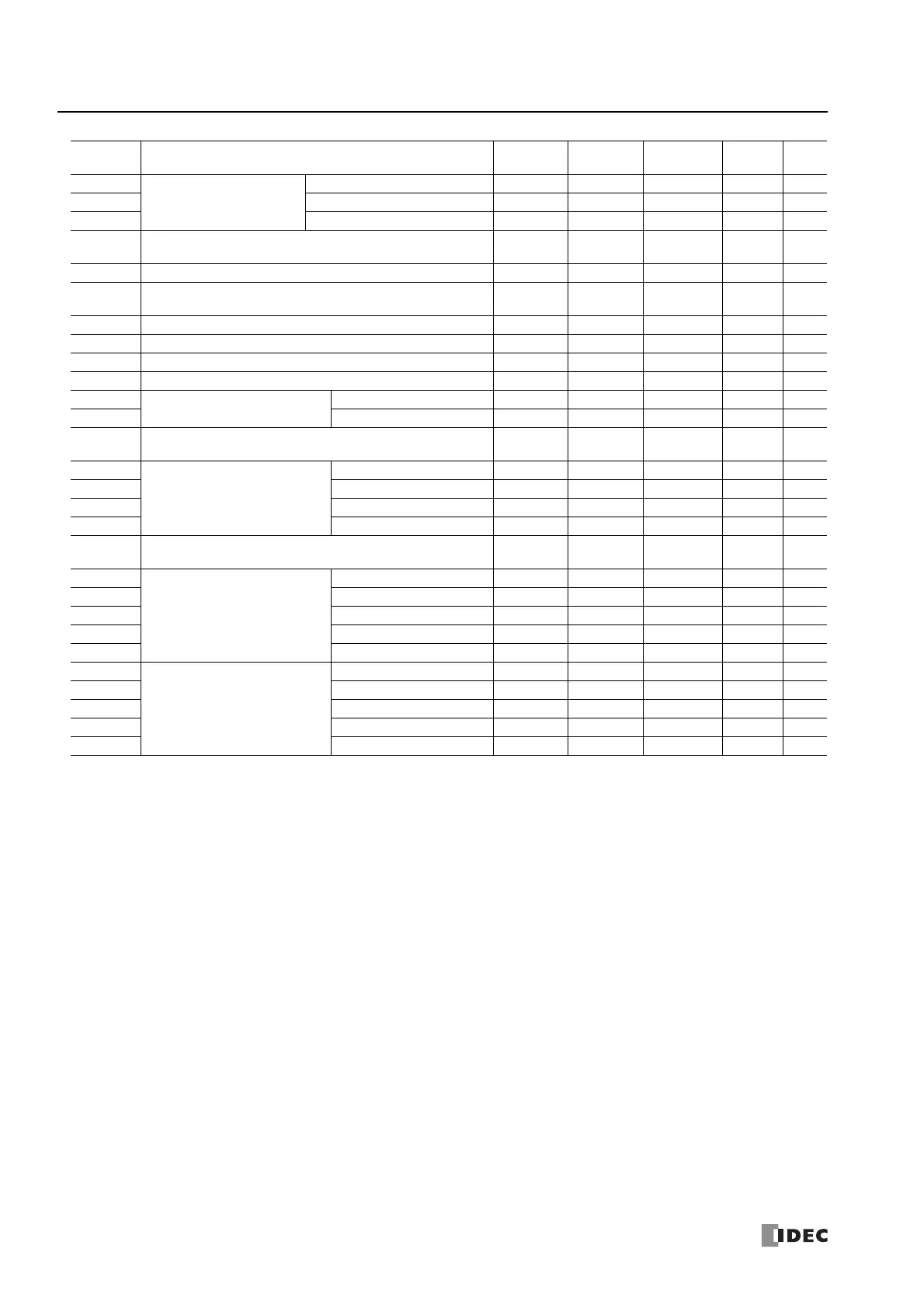

M8130

Disconnect User

Communication Connection

Connection 1 Maintained Cleared Read/Write X

M8131 Connection 2 Maintained Cleared Read/Write X

M8132 Connection 3 Maintained Cleared Read/Write X

M8133-

M8143

— Reserved —

M8144 Timer Interrupt Status (ON: Allowed, OFF: Prohibited) Cleared Cleared Read X

M8145-

M8147

— Reserved —

M8150 Comparison Result 1 Maintained Cleared Read X

M8151 Comparison Result 2 Maintained Cleared Read X

M8152 Comparison Result 3 Maintained Cleared Read X

M8153 — Reserved —

M8154

Data Register ROM Backup

Write Operating Cleared Read/Write X X

M8155 Read Operating Cleared Read/Write X X

M8156-

M8157

— Reserved —

M8160

Key Input Status

ESC Key + Up Key Cleared Cleared Read X X

M8161 ESC Key + Down Key Cleared Cleared Read X X

M8162 ESC Key + Left Key Cleared Cleared Read X X

M8163 ESC Key +Right Key Cleared Cleared Read X X

M8164

M8165

— Reserved —

M8166

High-speed Counter (Group5/I6)

Comparison Output Reset Cleared Cleared Read/Write X X

*

M8167 Gate Input Maintained Cleared Read/Write X X

*

M8170 Reset Input Maintained Cleared Read/Write X X

*

M8171 Comparison ON Status Maintained Cleared Read X X

M8172 Overflow Maintained Cleared Read X X

M8173

High-speed Counter (Group 6/I7)

Comparison Output Reset Cleared Cleared Read/Write X X

*

M8174 Gate Input Maintained Cleared Read/Write X X

*

M8175 Reset Input Maintained Cleared Read/Write X X

*

M8176 Comparison ON Status Maintained Cleared Read X X

M8177 Overflow Maintained Cleared Read X X

Device

Address

Description

CPU

Stopped

Power

OFF

Read/

Write

Ladder FBD

Loading...

Loading...