Datasheet, Volume 1 101

Electrical Specifications

Notes:

1. Unless otherwise noted, all specifications in this table apply to all processor frequencies.

2. V

IL

is defined as the maximum voltage level at a receiving agent that will be interpreted as a logical low

value.

3. V

IH

is defined as the minimum voltage level at a receiving agent that will be interpreted as a logical high

value.

4. V

IH

and V

OH

may experience excursions above V

DDQ

. However, input signal drivers must comply with the

signal quality specifications.

5. This is the pull up/down driver resistance.

6. R

TERM

is the termination on the DIMM and in not controlled by the Processor.

7. The minimum and maximum values for these signals are programmable by BIOS to one of the two sets.

8. SM_RCOMPx resistance must be provided on the system board with 1% resistors. SM_RCOMPx resistors

are to V

SS

.

9. DDR3 values are pre-silicon estimations and are subject to change.

10. SM_DRAMPWROK must have a maximum of 15 ns rise or fall time over V

DDQ

* 0.55 ±200 mV and the

edge must be monotonic.

11. SM_VREF is defined as V

DDQ

/2.

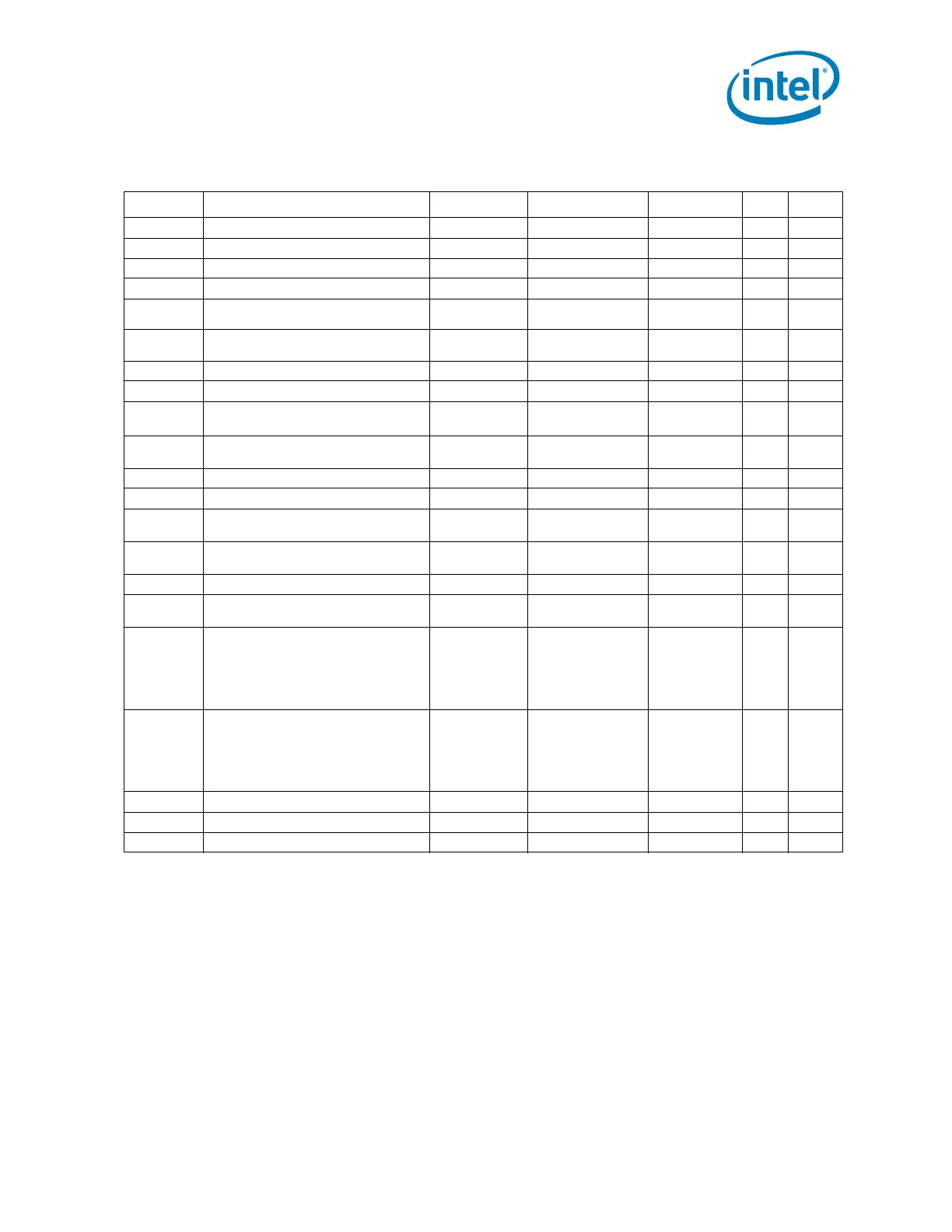

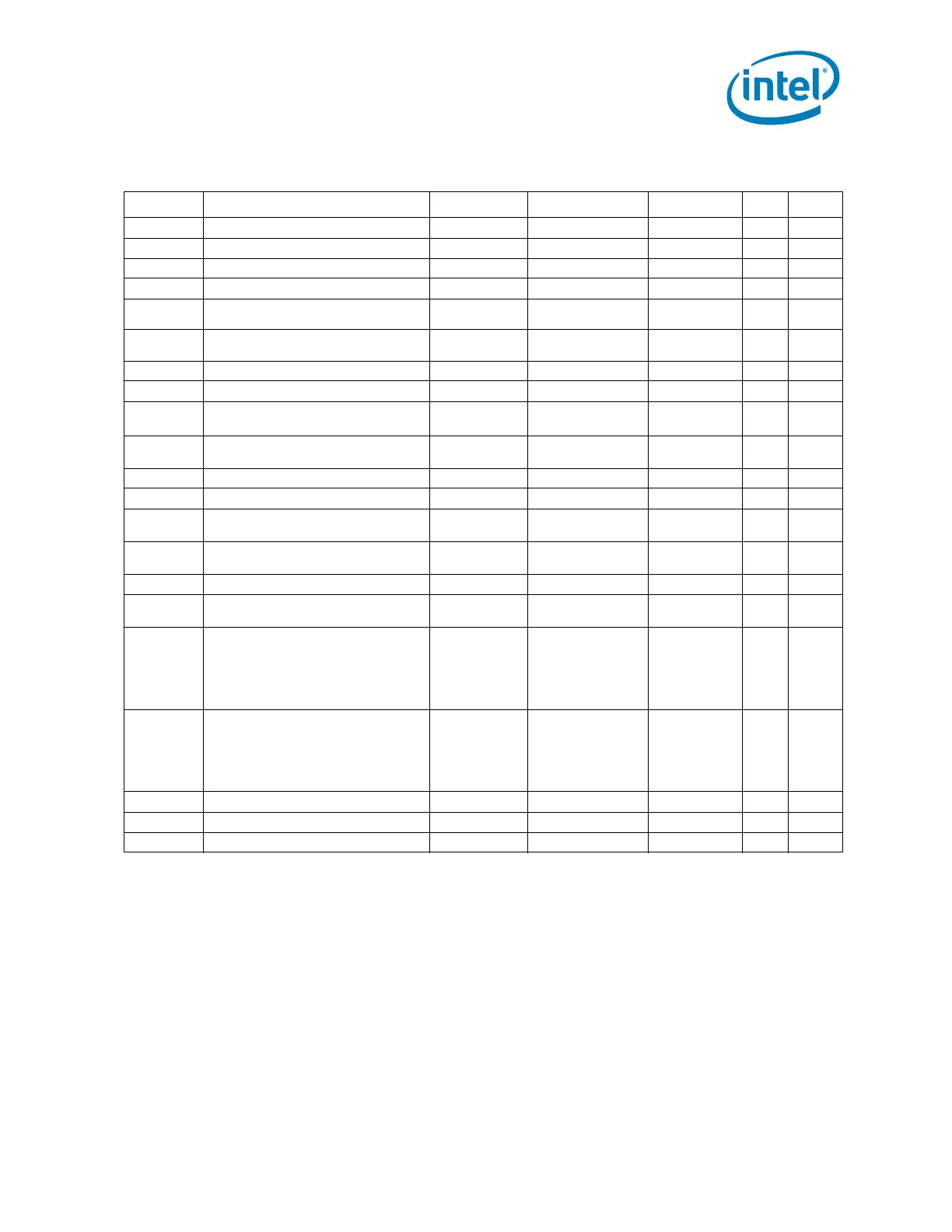

Table 7-11. DDR3 Signal Group DC Specifications

Symbol Parameter Min Typ Max Units Notes

1

V

IL

Input Low Voltage — — SM_VREF -0.1 V 2, 4, 11

V

IH

Input High Voltage SM_VREF + 0.1 — — V 3, 11

V

IL

Input Low Voltage (SM_DRAMPWROK) — — V

DDQ

*0.55 -0.1 V 10

V

IH

Input High Voltage (SM_DRAMPWROK) V

DDQ

*0.55 +0.1 — — V 10

V

OL

Output Low Voltage

—

(V

DDQ

/ 2)* (R

ON

/(R

ON

+R

TERM

))

—6

V

OH

Output High Voltage

—

V

DDQ

- ((V

DDQ

/ 2)*

(R

ON

/(R

ON

+R

TERM

))

—V4, 6

R

ON_UP(DQ)

DDR3 Data Buffer pull-up Resistance 24.31 28.6 31.46 5

R

ON_DN(DQ)

DDR3 Data Buffer pull-down Resistance 22.88 28.6 34.32 5

R

ODT(DQ)

DDR3 On-die termination equivalent

resistance for data signals

83

41.5

100

50

117

65

V

ODT(DC)

DDR3 On-die termination DC working

point (driver set to receive mode)

0.43*V

CC

0.5*V

CC

0.55*V

CC

V

R

ON_UP(CK)

DDR3 Clock Buffer pull-up Resistance 20.8 26 28.6 5

R

ON_DN(CK)

DDR3 Clock Buffer pull-down Resistance 20.8 26 31.2 5

R

ON_UP(CMD)

DDR3 Command Buffer pull-up

Resistance

16 20 22 5

R

ON_DN(CMD)

DDR3 Command Buffer pull-down

Resistance

16 20 24 5

R

ON_UP(CTL)

DDR3 Control Buffer pull-up Resistance 16 20 22 5

R

ON_DN(CTL)

DDR3 Control Buffer pull-down

Resistance

16 20 24 5

I

LI

Input Leakage Current (DQ, CK)

0V

0.2*V

DDQ

0.8*V

DDQ

V

DDQ

——

± 0.75

± 0.55

± 0.9

± 1.4

mA

I

LI

Input Leakage Current (CMD, CTL)

0V

0.2*V

DDQ

0.8*V

DDQ

V

DDQ

——

± 0.85

± 0.65

± 1.10

± 1.65

mA

SM_RCOMP0 Command COMP Resistance 138.6 140 141.4 8

SM_RCOMP1 Data COMP Resistance 25.74 26 26.26 8

SM_RCOMP2 ODT COMP Resistance 198 200 202 8

Loading...

Loading...