Electrical Specifications

104 Datasheet, Volume 1

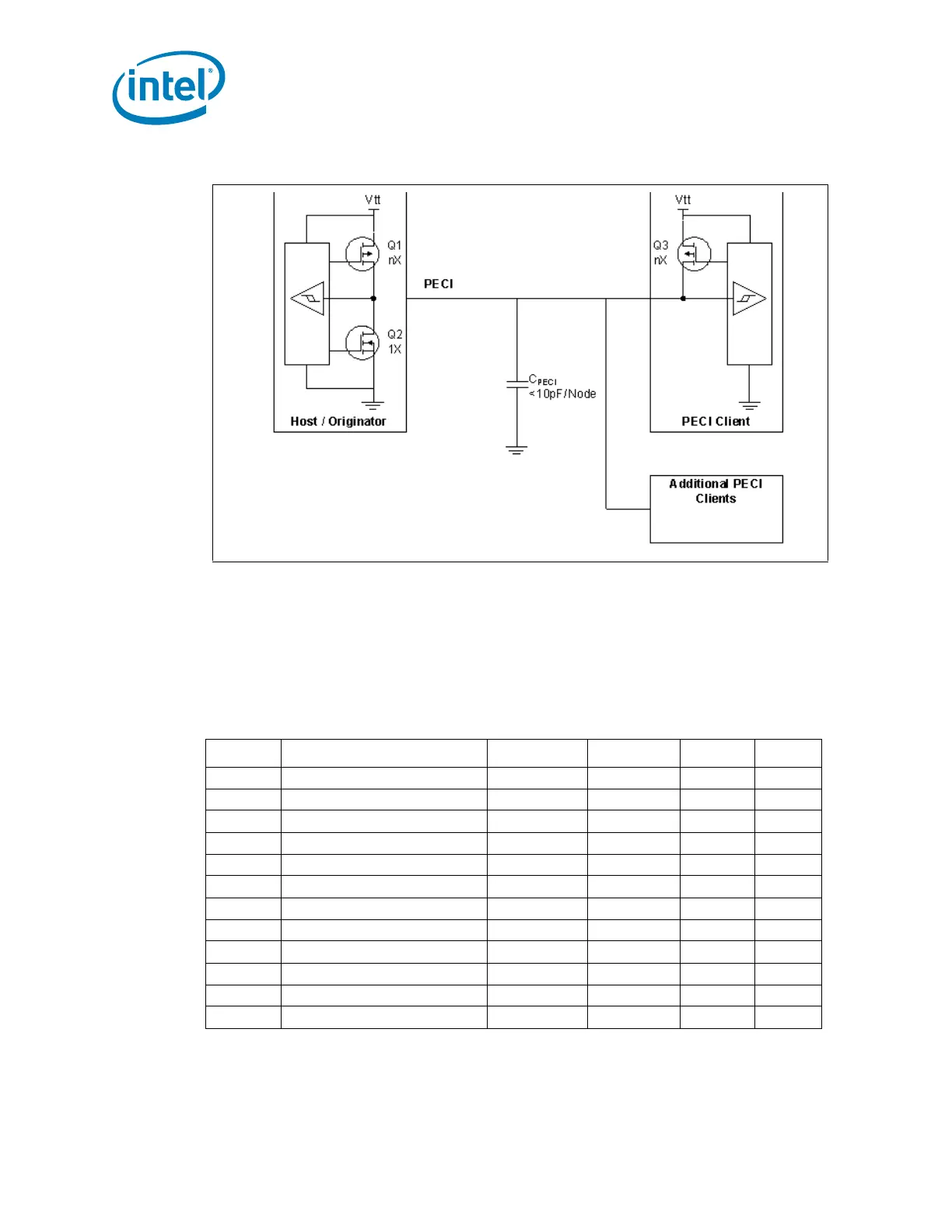

7.10.2 PECI DC Characteristics

The PECI interface operates at a nominal voltage set by V

CCIO

The set of DC electrical

specifications shown in Table 7-15 are used with devices normally operating from a

V

CCIO

interface supply. V

CCIO

nominal levels will vary between processor families. All

PECI devices will operate at the V

CCIO

level determined by the processor installed in the

system. For specific nominal V

CCIO

levels, refer to Table 7-6.

Notes:

1. V

CCIO

supplies the PECI interface. PECI behavior does not affect V

CCIO

min/max specifications.

2. The leakage specification applies to powered devices on the PECI bus.

3. The PECI buffer internal pull up resistance measured at 0.75*V

CCIO

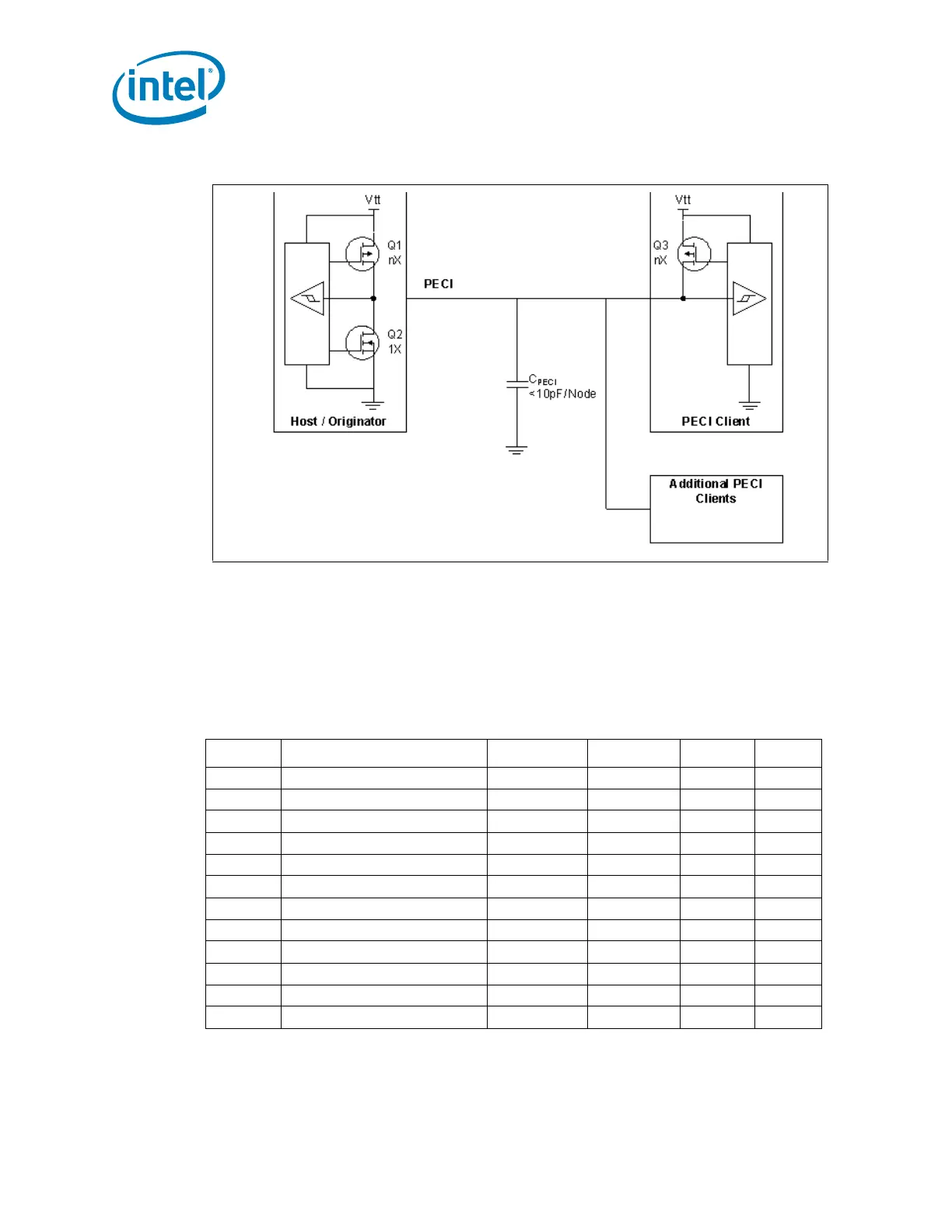

Figure 7-1. Example for PECI Host-clients Connection

Table 7-15. PECI DC Electrical Limits

Symbol Definition and Conditions Min Max Units Notes

1

Rup Internal pull up resistance 15 45 Ohm 3

V

in

Input Voltage Range -0.15 V

CCIO

V

V

hysteresis

Hysteresis 0.1 * V

CCIO

N/A V

V

n

Negative-Edge Threshold Voltage 0.275 * V

CCIO

0.500 * V

CCIO

V

V

p

Positive-Edge Threshold Voltage 0.550 * V

CCIO

0.725 * V

CCIO

V

C

bus

Bus Capacitance per Node N/A 10 pF

Cpad Pad Capacitance 0.7 1.8 pF

Ileak000 leakage current @ 0V — 0.6 mA 2

Ileak025 leakage current @ 0.25*V

CCIO

—0.4mA2

Ileak050 leakage current @ 0.50*V

CCIO

—0.2mA2

Ileak075 leakage current @ 0.75*V

CCIO

—0.13mA2

Ileak100 leakage current @ V

CCIO

—0.10mA2

Loading...

Loading...