Chapter

7.

Interrupts

7-2

The

8080

contains a bit named

INTE

w:,ich may

be

set or reset

by

the instructions

EI

and

DI

described

in

Chapter 3. Whenever INTE

is

equal to 0, the entire interrupt handling system

is

disabled, and no interrupts

wi

II

be

accepted.

When

the

8080

recognizes

an

interrupt request from

an

external device, the following actions occur:

1.

The instruction currently being executed

is

completed.

2.

The interrupt enable bit, INTE,

is

reset =

O.

3.

The interrupting device supplies,

via

hardware, one instruction which the

CPU

executes. This

instruction does not appear anywhere

in

memory, and the programmer has

no

control over it,

since it

is

a function

of

the interrupting device's controller design. The program counter

is

not

i ncremen ted before this instruct ion.

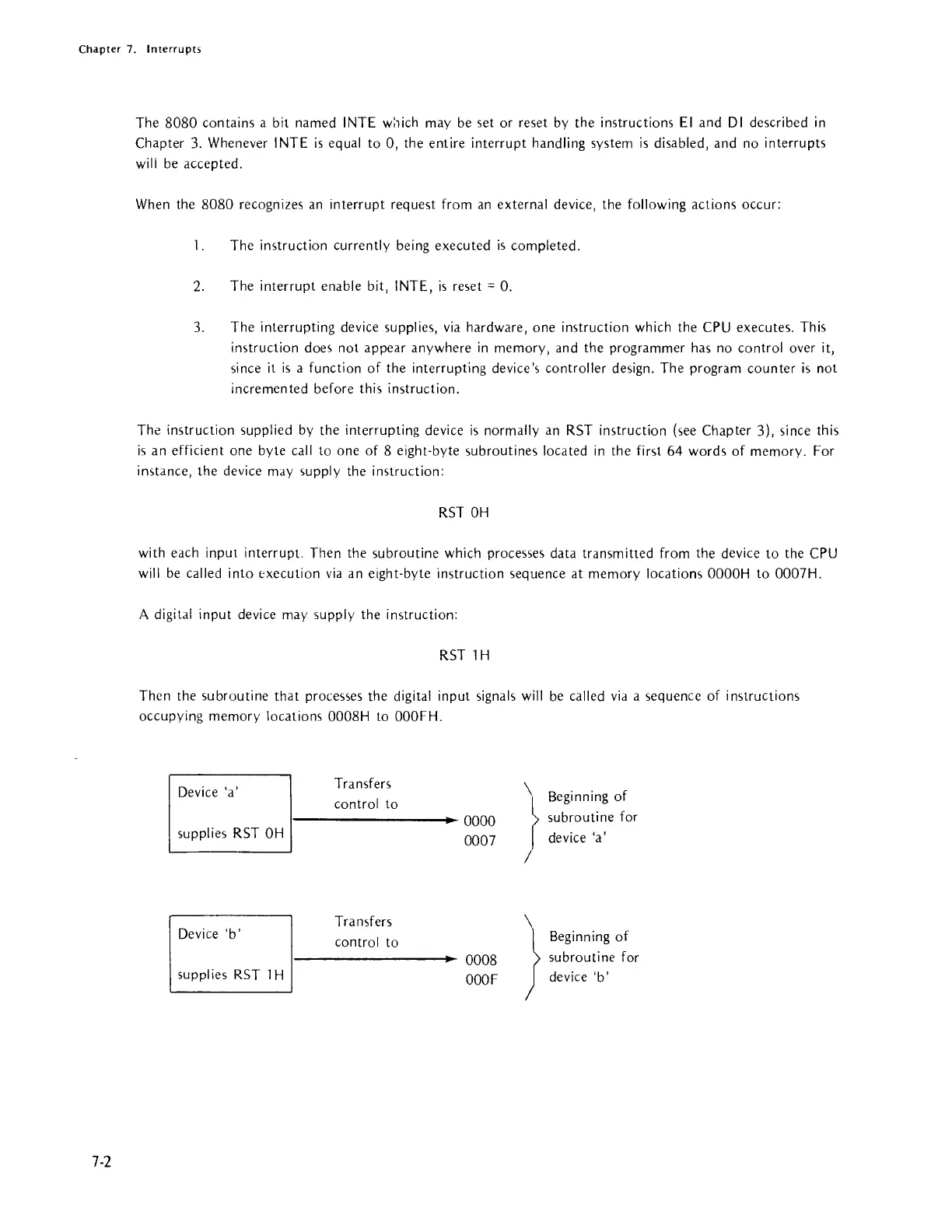

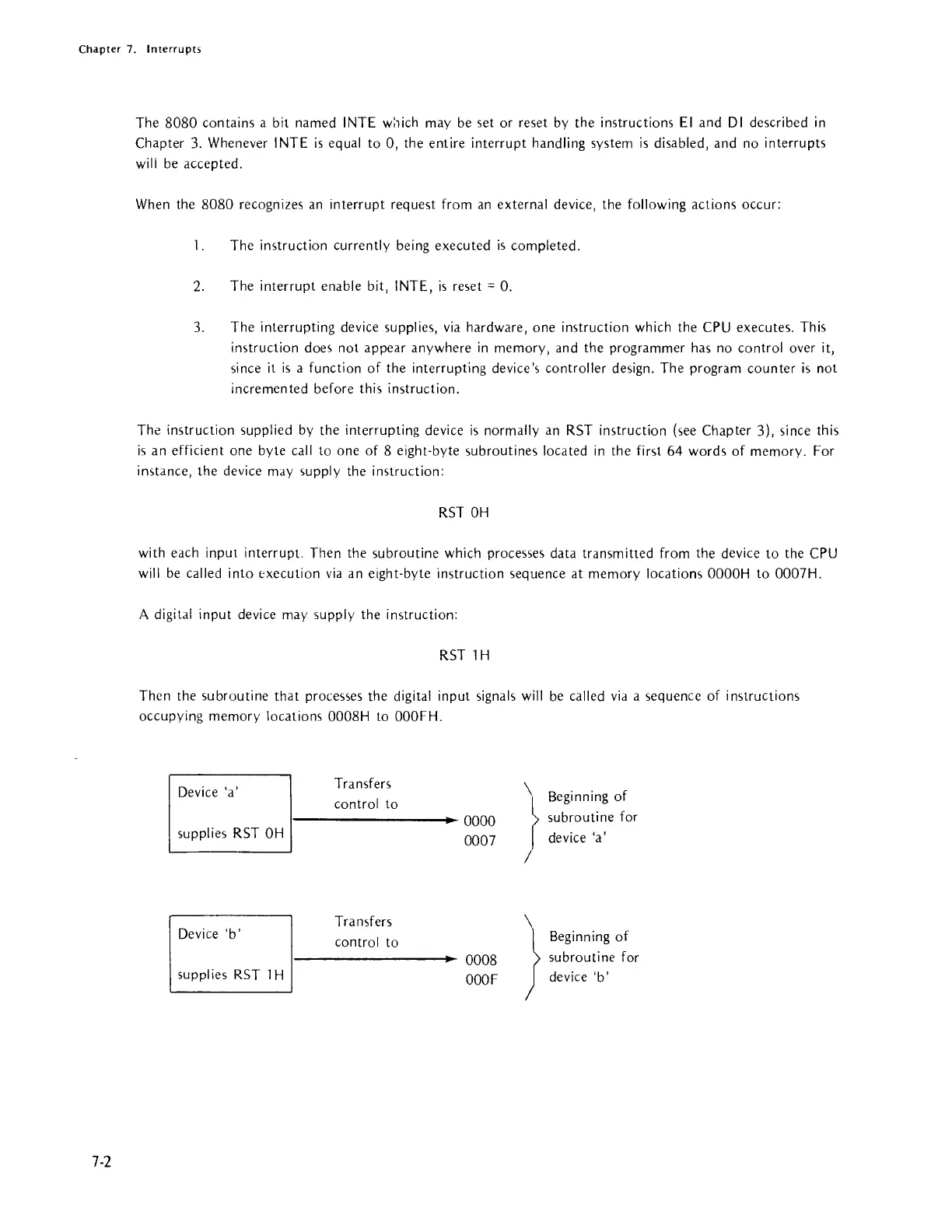

The instruction supplied

by

the interrupting device

is

normally

an

RST

instruction (see Chapter 3), since this

is

an efficient one byte

call

to one of 8 eight-byte subroutines located

in

the first 64 words

of

memory. For

instance, the device

may supply the instruction:

RST

OH

with each input interrupt. Then the subroutine which processes data transmitted from the device to the

CPU

will

be

called into l:xecution

via

an eight·byte instruction sequence at memory locations

OOOOH

to 0007H.

A digital input device may supply the instruction:

RST

lH

Then the subroutine that processes the digital input signals

will

be

called

via

a sequence of instructions

occupying memory locations

0008H to

OOOFH.

Device 'a'

supplies RST

OH

Device

'b'

supplies RST 1 H

Transfers

control to

-------~.

0000

0007

Transfers

control to

•

0008

OOOF

\/~

Beginning

of

subroutine for

device 'a'

}

Beginning

of

subroutine for

device

'b'

Loading...

Loading...