Chapter 1. Assembly language and Processors

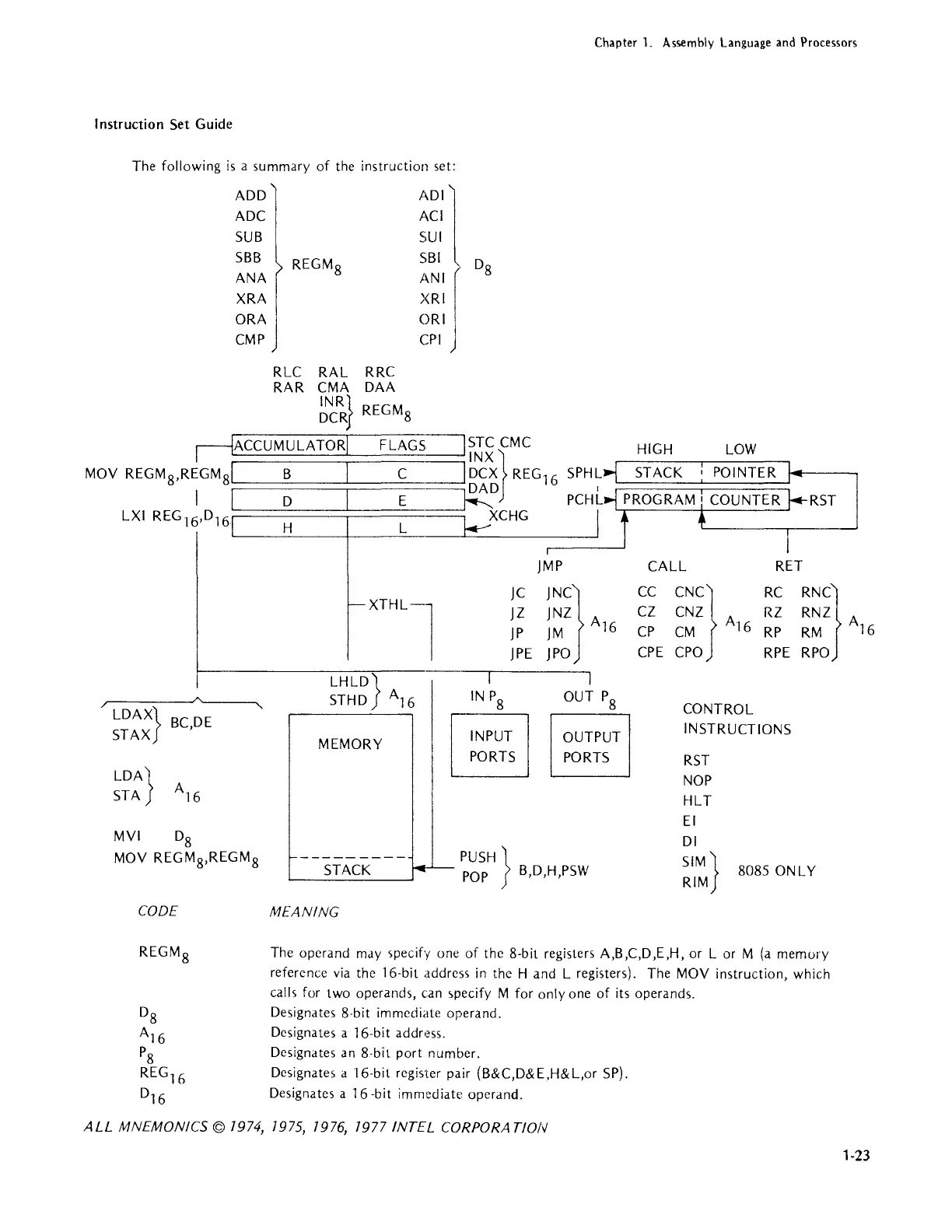

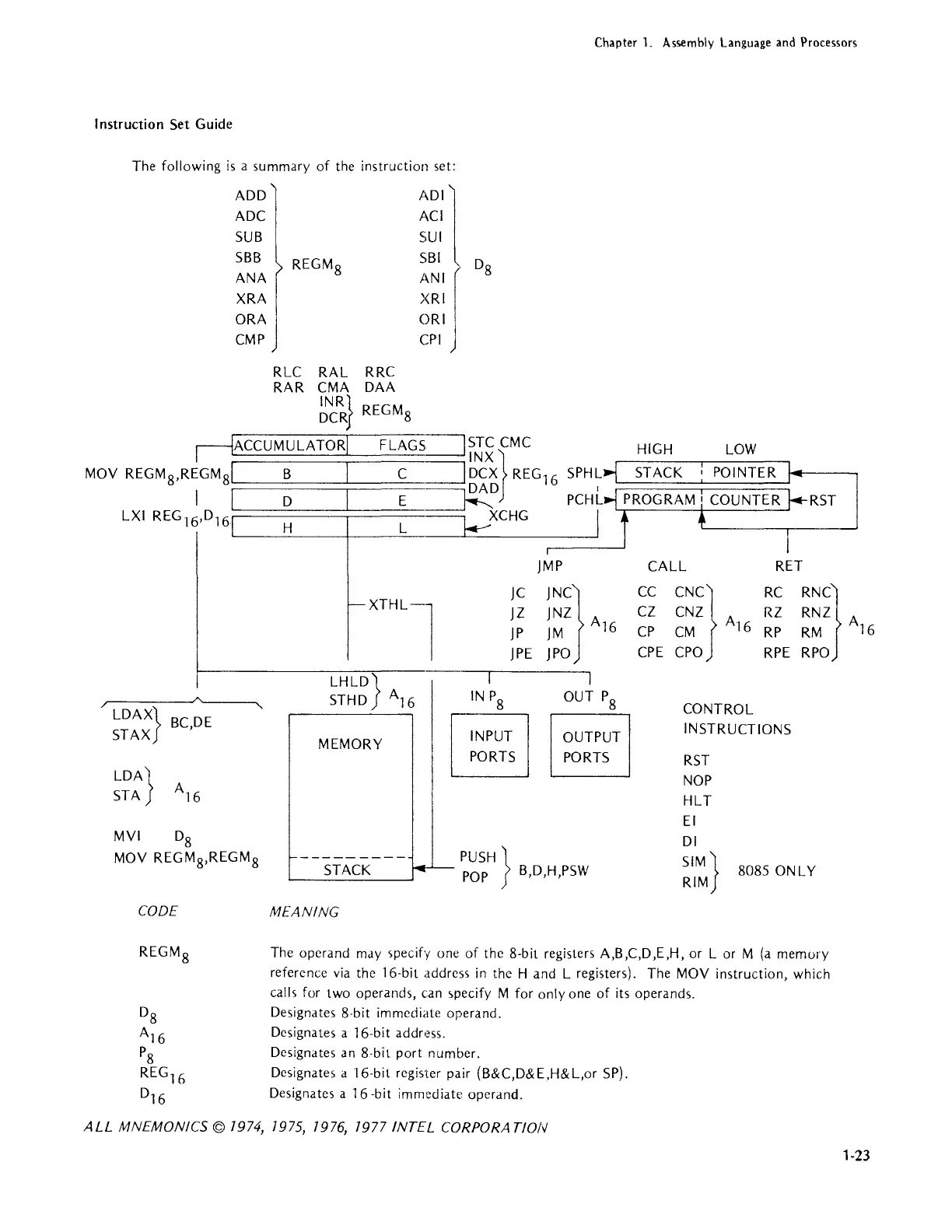

Instruction Set Guide

The following

is

a summary of the instruction set:

ADD

ADC

ACI

SUB

SUI

ADll

SBB

REGM

g

~~l

f

D8

ANA

XRA

)(RI

ORA ORI

CMP

CPI

RLC

RAL RRC

RAR

CMA

DAA

INR}

DCR

REGM

g

~ACCUMULATORI

FLAGS

MOY

REGMg,REGMgl B I C

I I D I

LXI

REG

16

,D

16

E

H L

]STC

CMC

INX}

JDCX

REG

16

SPHL

DAD

I

~

PCHL

k

XCHG

I

JMP

HIGH

LOW

STACK

RST

CALL

RET

JC

JZ

JP

JPE

JNZ

A

JNC}

JM

16

CZ

CNZ

A

CC

CNC}

CP

CM

16

RZ

RNZ

A

RC

RNC}

RP

RM

16

/

A

,

LDAX}

BC,DE

STAX

LDA}

STA

A

16

MYI

Dg

MOY

REGMg,REGM

g

CODE

REGM

g

LHLD}

STHD

A

16

MEMORY

[

INPUT

PORTS

JPO

I

OUT

P

g

OUTPUT

PORTS

f---STACK---

...

__

~~~H}

B,D,H,PSW

MEANING

CPE

CPO

RPE

RPO

CONTROL

INSTRUCTIONS

RST

NOP

HLT

EI

DI

SIM}

gOg5

ONLY

RIM

The opcrand

may

specify one of thc g-bit registers A,B,C,D,E,H, or L

or

M

(a

memory

refercnce

via

thc 16-bit addrcss

in

the

Hand

L registers). The

MOY

instruction, which

calls for two operands, can

~pecify

M for only one of

its

operands.

Designates

g·bit immcdiatc operand.

Dcsigna

tes a 16-bit address.

Dcsignates an g-bit port numbcr.

Dcsignates a 16-bit

rcgisTer

pair (B&C,D&E.H&L,or SP).

Dcsignatcs a 16 -bit immediatE' opcrand.

ALL

MNEMONICS © 7974, 7975, 7976, 7977

INTEL

CORPORA

TlON

1-23

Loading...

Loading...