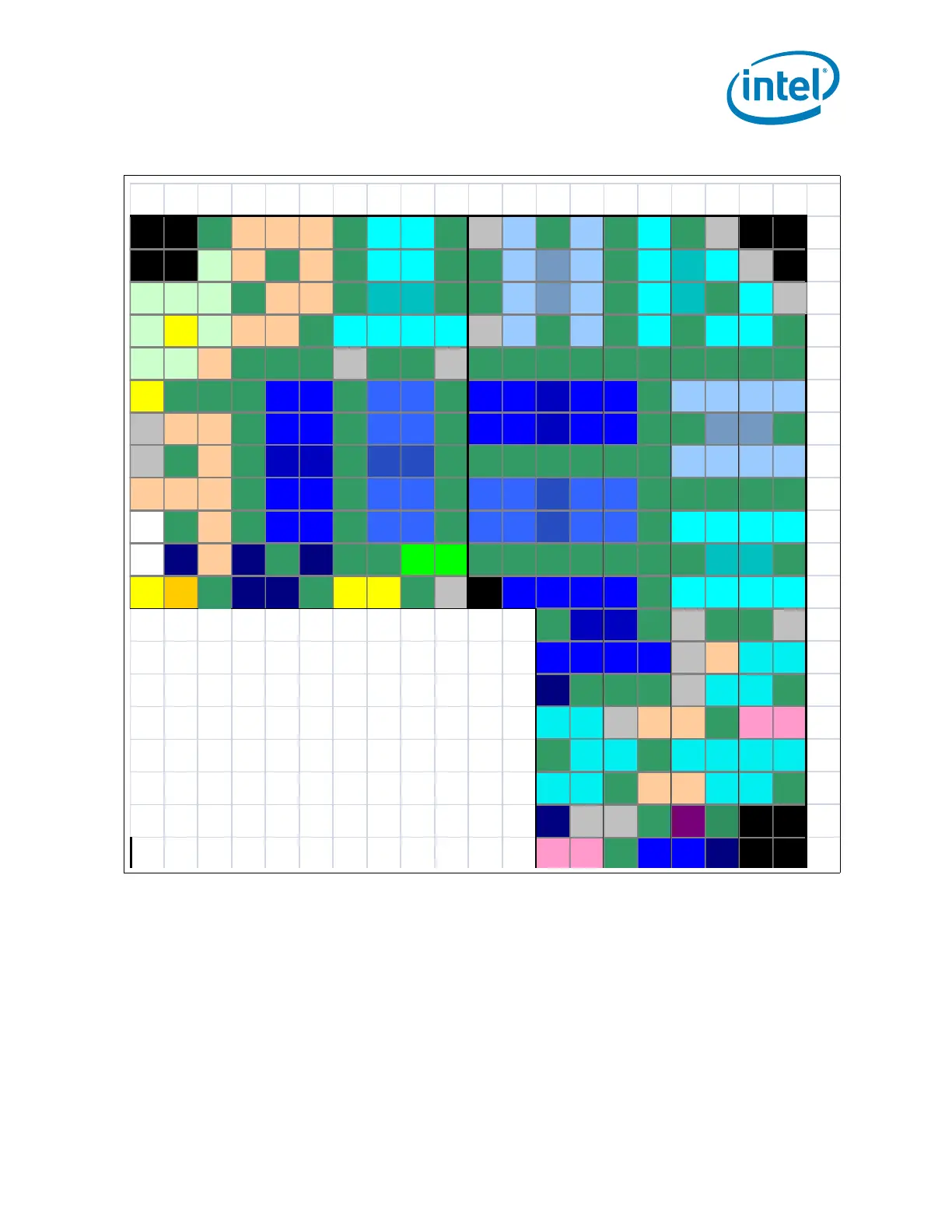

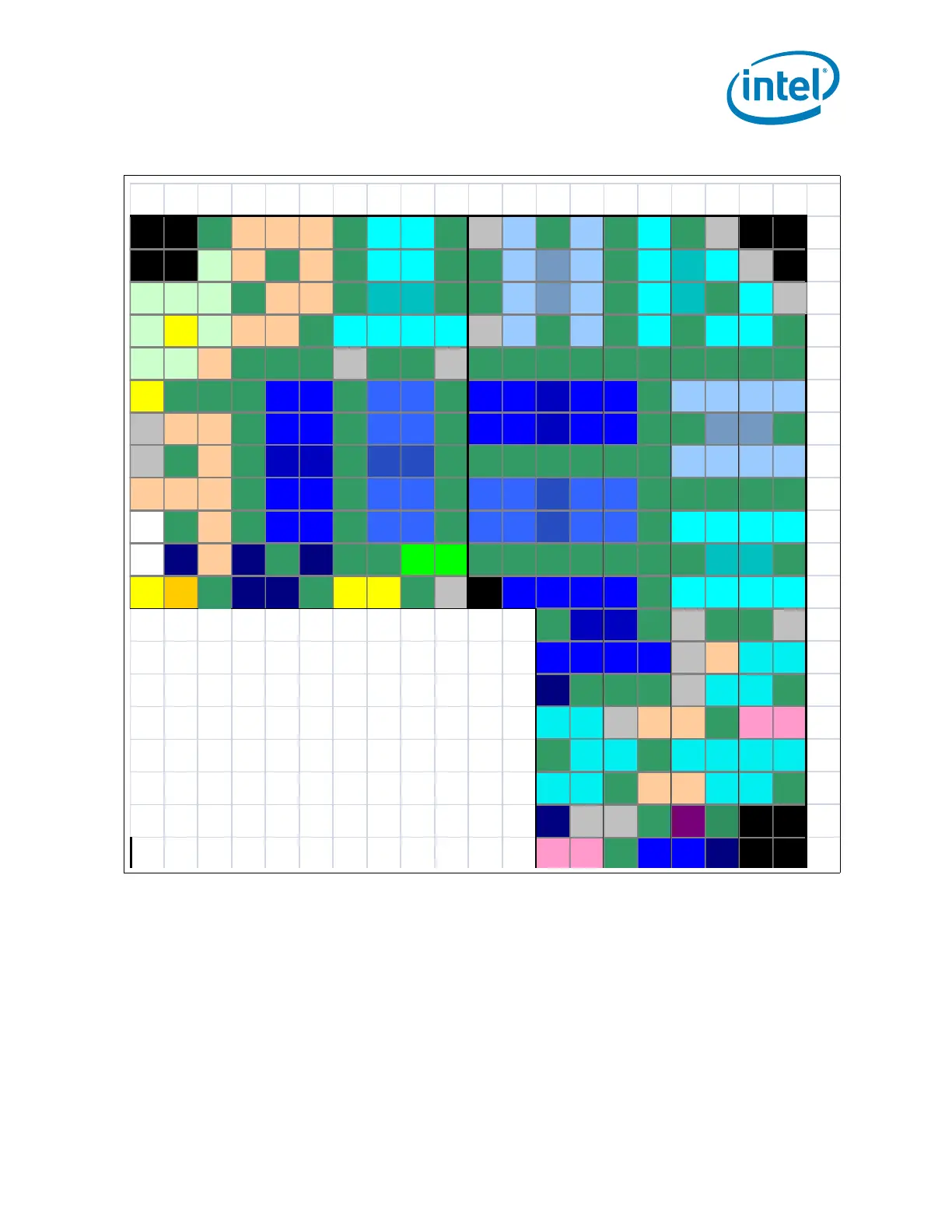

Figure 8-2. Socket Pinmap (Top View, Upper-Right Quadrant)

20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

VSS

SB_MA[9] SB_ MA[14]

SB_CKE[1]

VSS

RSVD RSVD

VSS

RSVD

SA_DQ[31]

VSS

SA_DQ[24]

VSS

SA_DQ[23]

VSS

RSVD_NCTF

AY

SM _DRAM RST #

SB_BS[2]

VSS

SB_CKE[2]

VSS

RSVD RSVD

VSS VSS

SA_DQ[30]

SA_DQS#[3]

SA_DQ[29]

VSS

SA_DQ[19] SA_DQS[2] SA_DQ[17] RSVD_NCTF

AW

SA_BS[2]

SA_CKE[0] SA_CKE[3]

VSS

SB_MA[15 ]

SB_CKE[3]

VSS

SA_DQS[8]

SA_DQS#[8]

VSS VSS

SA_DQ[26] SA_DQS[3] SA_DQ[28]

VSS

SA_DQ[18]

SA_DQS#[2]

VSS

SA_DQ[16] RSVD_NCTF

AV

SA_MA[14]

VDDQ

SA_CKE[2] SB_MA[11 ]

SB_CKE[0]

VSS

RSVD RSVD RSVD RSVD RSVD

SA_DQ[27]

VSS

SA_DQ[25]

VSS

SA_DQ[22]

VSS

SA_DQ[21] SA_DQ[20]

VSS

AU

SA_MA[15] SA_CKE[1] SB_MA[12]

VSS VSS VSS

RSVD

VSS VSS

RSVD

VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS

AT

VDDQ

VSS VSS VSS

RSVD RSVD

VSS

SB_DQ[26] SB_DQ[30]

VSS

SB_DQ[19] SB_DQ[23] SB_DQS[2] SB_DQ[17] SB_DQ[21]

VSS

SA_DQ[11] SA_DQ[10] SA_DQ[1 4] SA_DQ[15]

AR

RSVD

SB_MA[4] SB_MA[5]

VSS

RSVD RSVD

VSS

SB_DQ[27] SB_DQ[31]

VSS

SB_DQ[18] SB_DQ[22]

SB_DQS#[2]

SB_DQ[16] SB_DQ[20]

VSS VSS

SA_DQS[1]

SA_DQS#[1]

VSS

AP

RSVD

VSS

SB_MA[8]

VSS

SB_DQS[8]

SB_DQS#[8]

VSS

SB_DQS[3]

SB_DQS#[3]

VSS VSS VSS VSS VSS VSS VSS

SA_D Q [9]

SA_DQ[13] SA_DQ[12]

SA_D Q[8]

AN

SB_MA[1] SB_MA[2] SB_MA[6]

VSS

RSVD RSVD

VSS

SB_DQ[25] SB_DQ[24]

VSS

SB_DQ[10] SB_DQ[15] SB_DQS[1]

SB_D Q[9]

SB_DQ[13]

VSS VSS VSS VSS VSS

AM

SB_CK[1]

VSS

SB_MA[7]

VSS

RSVD RSVD

VSS

SB_DQ[29] SB_DQ[28]

VSS

SB_DQ[11] SB_DQ[14]

SB_DQS#[1]

SB_D Q[8]

SB_DQ[12]

VSS

SA_DQ[3] SA_DQ[2] SA_DQ[6] SA_DQ[7]

AL

SB_CK#[1]

VCCIO

SB_MA[3]

VCCIO

VSS

VCCIO

VSS VSS

VCCPLL VCCPLL

VSS VSS VSS VSS VSS VSS VSS

SA_DQS[0]

SA_DQS#[0]

VSS

AK

VDDQ

SM _D RAM PW RO K

VSS

VCCIO VCCIO

VSS

VDDQ VDDQ

VSS

RSVD

SB_DQ[2]

SB_DQ [3] SB_DQ[7] SB_DQ[6]

VSS

SA_DQ[1] SA_DQ[0] SA_DQ[4] SA_DQ[5]

AJ

VSS

SB_DQS[0]

SB_DQS#[0]

VSS

FC_ AH 4

VSS VSS

FC_ AH 1

AH

SB_DQ[1] SB_DQ[0] SB_DQ[5] SB_DQ[4]

RSVD

FD I _ I NT

FDI_TX[7]

FDI _ TX #[ 7]

AG

VCCIO

VSS VSS VSS

RSVD

FDI_TX[6]

FDI _TX #[ 6 ]

VSS

AF

FDI _TX #[ 5 ]

FDI_TX[5]

RSVD

FDI_FSYNC[1] FDI_LSYNC[1]

VSS

FDI_COMPIO FDI_ICOMPO

AE

VSS

FDI_TX[4]

FDI _TX #[ 4 ]

VSS

FDI_TX[3]

FDI _ TX #[ 3]

FDI_TX[2]

FDI _ TX #[ 2]

AD

FDI_TX[0]

FDI _ TX #[ 0]

VSS

FDI_FSYNC[0] FDI_LSYNC[0]

FDI _ TX #[ 1]

FDI_TX[1]

VSS

AC

VCCIO RSVD RSVD

VSS

VCCIO_SE NSE VSSIO_ SENSE

AB

DMI_TX#[3] DMI_TX[3]

VSS

DM I_ RX#[3 ]

DMI_RX[3]

VCCIO

AA

Loading...

Loading...