Product Description

29

1.8.3 IDE Support

1.8.3.1 IDE Interfaces

The ICH2’s IDE controller has two independent bus-mastering IDE interfaces that can be

independently enabled. The IDE interfaces support the modes listed in Table 7.

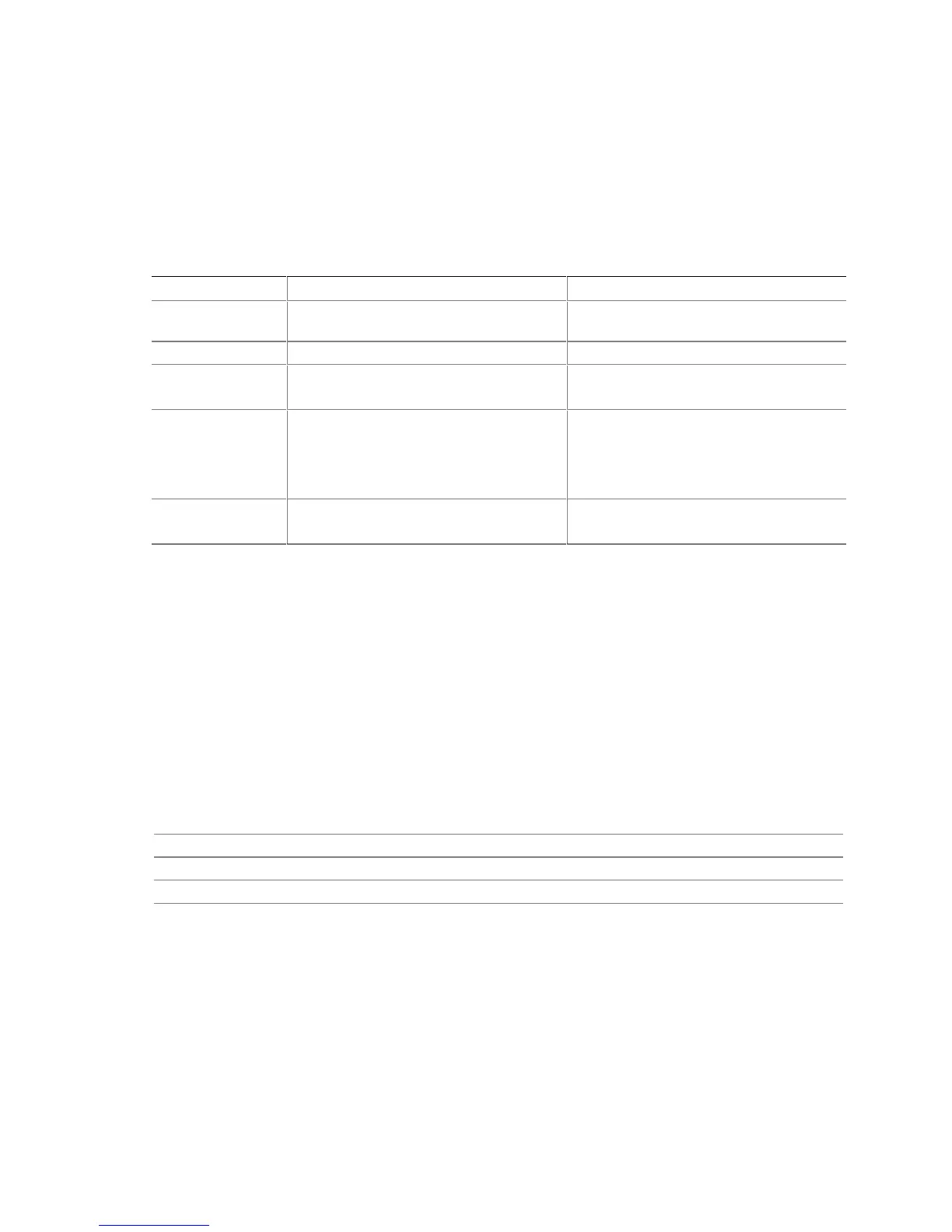

Table 7. Supported IDE Modes

Mode Description Supported Transfer Rates

Programmed I/O

(PIO)

Processor controls data transfer

8237-style DMA DMA offloads the processor Up to 16 MB/sec

Ultra DMA • DMA protocol on the IDE bus

• Supports host and target throttling

Up to 33 MB/sec

ATA-66 • DMA protocol on the IDE bus

• Allows host and target throttling

• Similar to Ultra DMA

• Device driver compatible

Up to 66 MB/sec

ATA-100 • DMA protocol on the IDE bus

• Allows host and target throttling

• Read transfer rates up to 100 MB/sec

• Write transfer rates up to 88 MB/sec

✏ NOTE

ATA-66 and ATA-100 are faster timings and require a specialized cable to reduce reflections,

noise, and inductive coupling.

The IDE interfaces also support ATAPI devices (such as CD-ROM drives) and ATA devices using

the transfer modes listed in Section 4.4.4.1 on page 105.

The BIOS supports Logical Block Addressing (LBA) and Extended Cylinder Head Sector (ECHS)

translation modes. The drive reports the transfer rate and translation mode to the BIOS.

The D850MD and D850MV boards support Laser Servo (LS-120) diskette technology through the

IDE interfaces. An LS-120 drive can be configured as a boot device in the BIOS Setup program.

For information about Refer to

The location of the IDE connectors Figure 15, page 63

The signal names of the IDE connectors Table 41, page 69

The Boot menu in the BIOS Setup program Section 4.7, page 113

Loading...

Loading...