Datasheet

29

Electrical Specifications

3.4 Catastrophic Thermal Protection

The processor supports the THERMTRIP# signal for catastrophic thermal protection. An

external thermal sensor should also be used to protect the processor and the system

against excessive temperatures. Even with the activation of THERMTRIP#, which halts

all processor internal clocks and activity, leakage current can be high enough that the

processor cannot be protected in all conditions without the removal of power to the

processor. If the external thermal sensor detects a catastrophic processor temperature

of approximately 125°C (maximum), or if the THERMTRIP# signal is asserted, the V

CC

supply to the processor must be turned off within 500 ms to prevent permanent silicon

damage due to thermal runaway of the processor. THERMTRIP# functionality is not

ensured if the PWRGOOD signal is not asserted, and during Deep Power Down

Technology State (C6).

3.5 Reserved and Unused Pins

All RESERVED (RSVD) pins must remain unconnected. Connection of these pins to V

CC

,

V

SS

, or to any other signal (including each other) can result in component malfunction

or incompatibility with future processors. See Section 4.2 for a pin listing of the

processor and the location of all RSVD pins.

For reliable operation, always connect unused inputs or bidirectional signals to an

appropriate signal level. Unused active low AGTL+ inputs may be left as no-connects if

AGTL+ termination is provided on the processor silicon. Unused active high inputs

should be connected through a resistor to ground (V

SS

). Unused outputs can be left

unconnected. The TEST1,TEST2,TEST3,TEST4,TEST5,TEST6,TEST7 pins are used for

test purposes internally and can be left as “No Connects”.

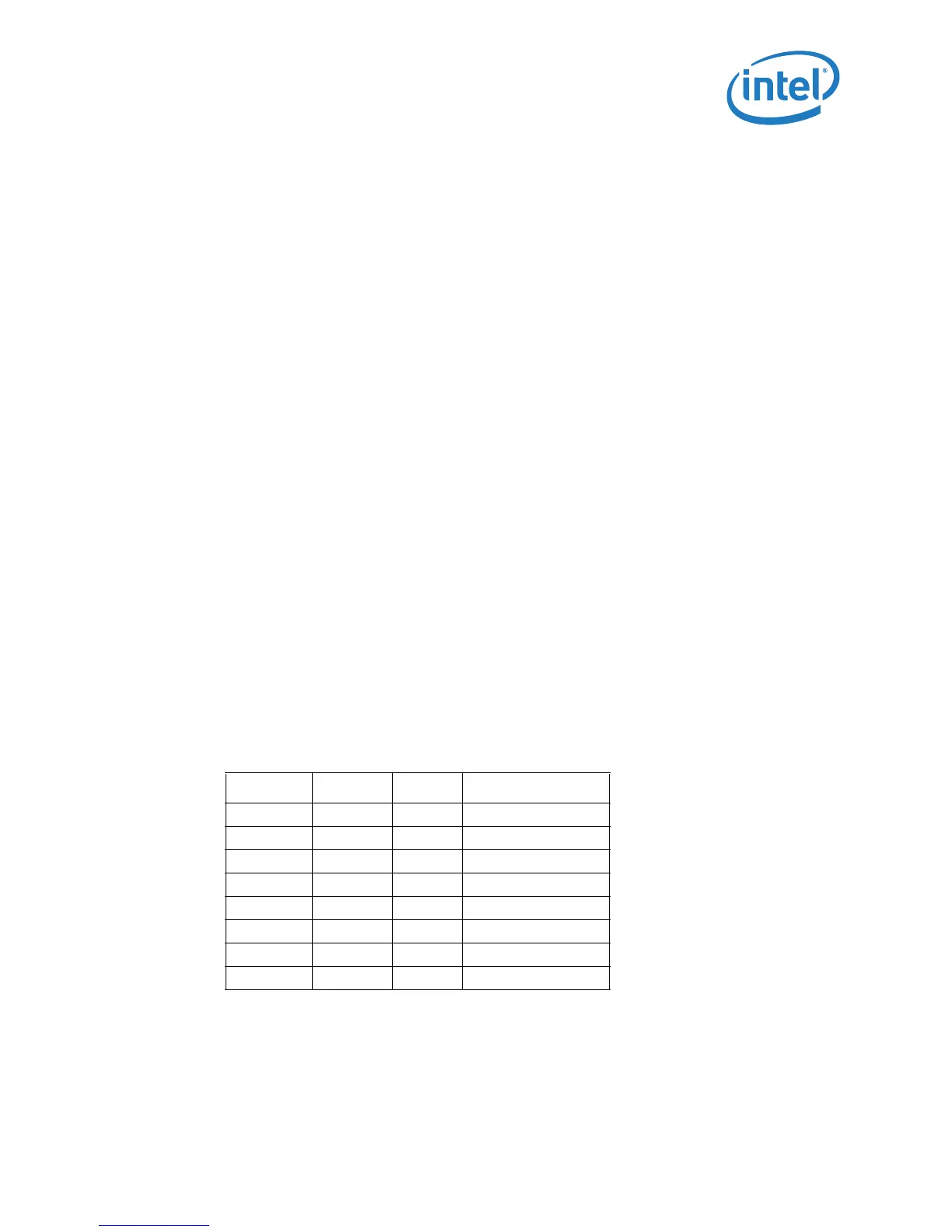

3.6 FSB Frequency Select Signals (BSEL[2:0])

The BSEL[2:0] signals are used to select the frequency of the processor input clock

(BCLK[1:0]). These signals should be connected to the clock chip and the appropriate

chipset on the platform. The BSEL encoding for BCLK[1:0] is shown in Tabl e 3.

Table 3. BSEL[2:0] Encoding for BCLK Frequency

BSEL[2] BSEL[1] BSEL[0] BCLK Frequency

L L L 266 MHz

L L H RESERVED

L H H RESERVED

L H L 200 MHz

H H L RESERVED

H H H RESERVED

H L H RESERVED

H L L RESERVED

Loading...

Loading...