SCPI Status Register

Copyright © ITECH Electronic Co., Ltd. 14

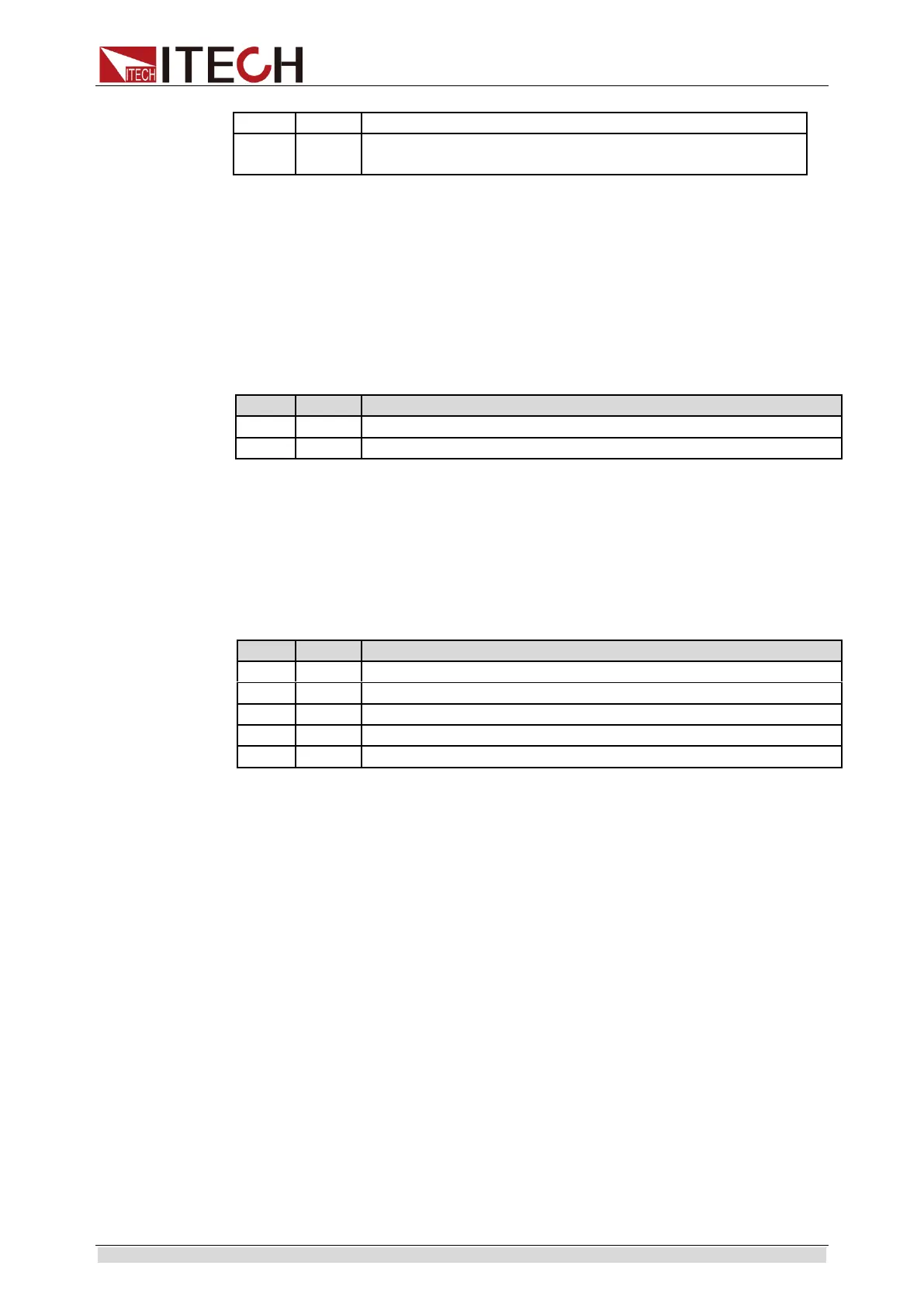

the range of 199 through 100 can set this bit.

The unit has been turned off and then on since this bit

was last read.

Operation Status Register Group

The operational status register group consists of three 16-bit registers: status

register, event register, and enable register. When the status register

corresponding bit is changed, the corresponding event register bit will be set. If

the corresponding bit in the enable register bit is set, it will be generated once

Event (status byte register OPER is set). After executing an event register read

operation, the event register will be automatically cleared. The status register is

defined as follows:

The electronic load iscalculated a new calibration constant.

The electronic load is waiting for a trigger.

Status Byte Register Group

The status byte register group consists of two 8-bit registers: event register and

enable register. If the corresponding bit in the enable register bit is set, it will be

generated once Event (status byte register RQS is set). The status byte register

will be automatically cleared when an event register read is executed. The

status register is defined as follows:

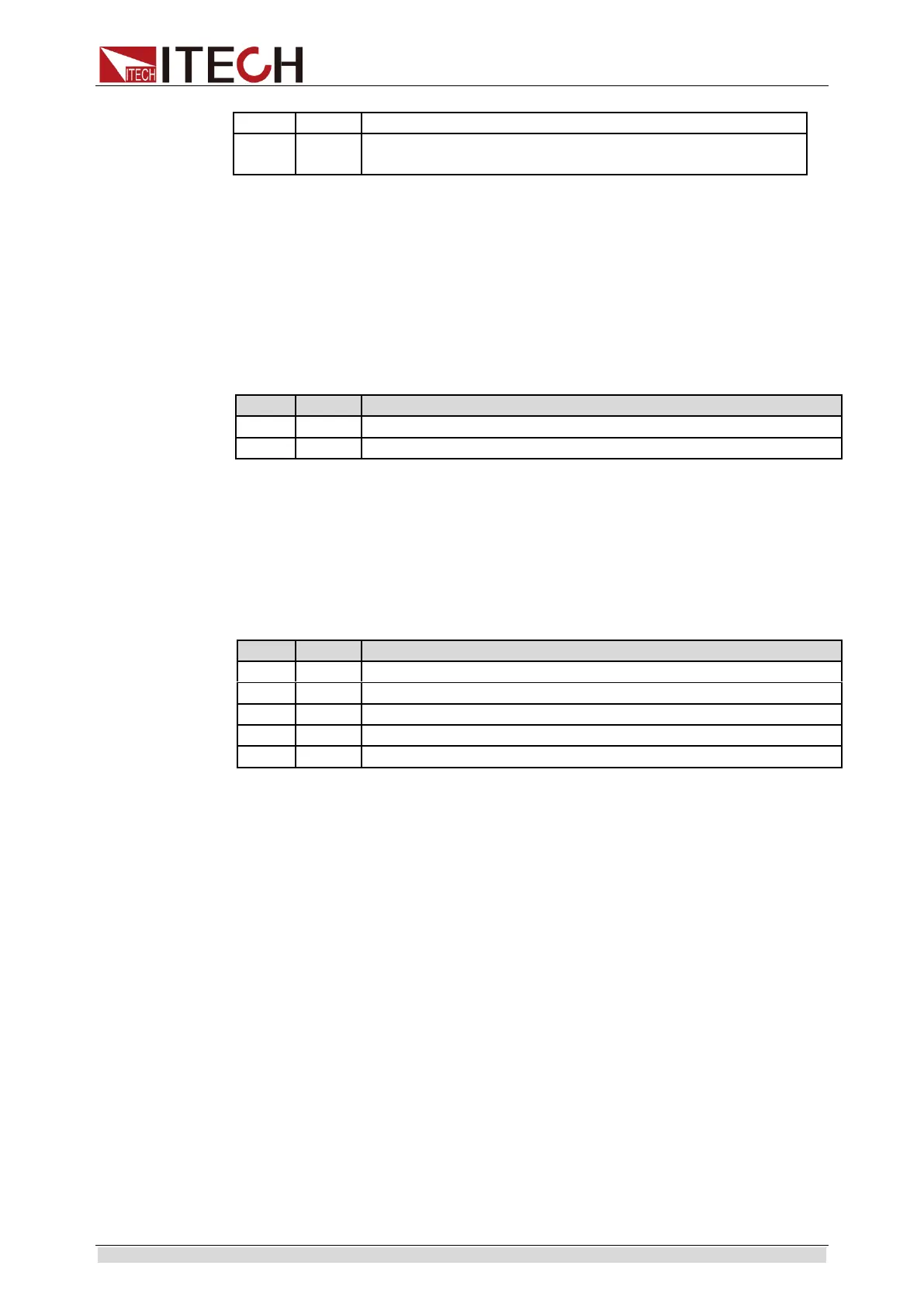

Indicates if an enabled questionable event has occurred.

Indicates if the Output Queue contains data.

Indicates if an enabled standard event has occurred.

During a serial poll, RQS is returned and cleared.

Indicates if an operation event has occurred.

Loading...

Loading...