S530 Parametric Test System Test Subroutine Library User's Manual Section 3: Test subroutine library reference

S530-907-01 Rev. A / September 2015 3-3

beta2

This subroutine calculates beta () and base-emitter voltage (V

BE

) at a specified collector current (I

C

) and

collector-emitter bias (V

CE

).

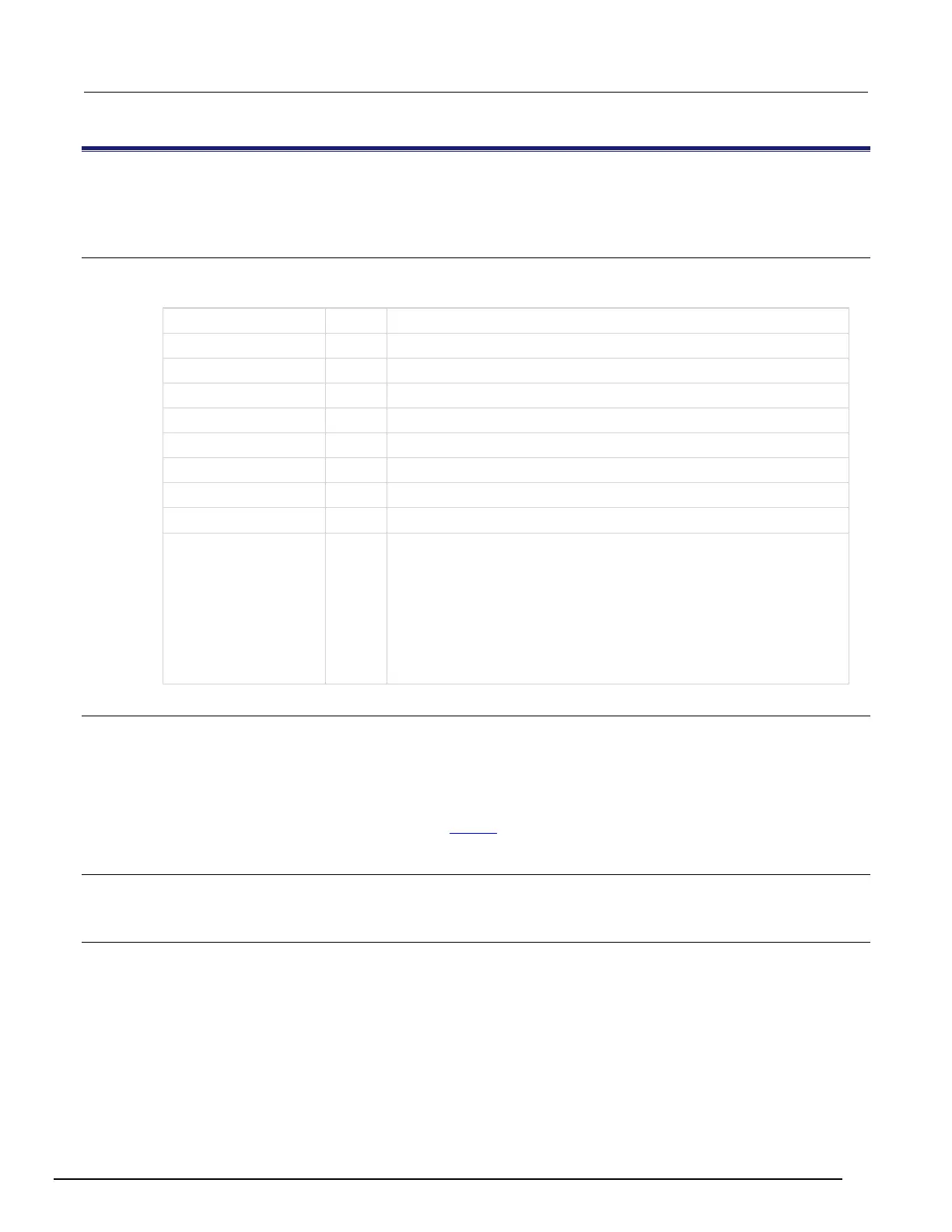

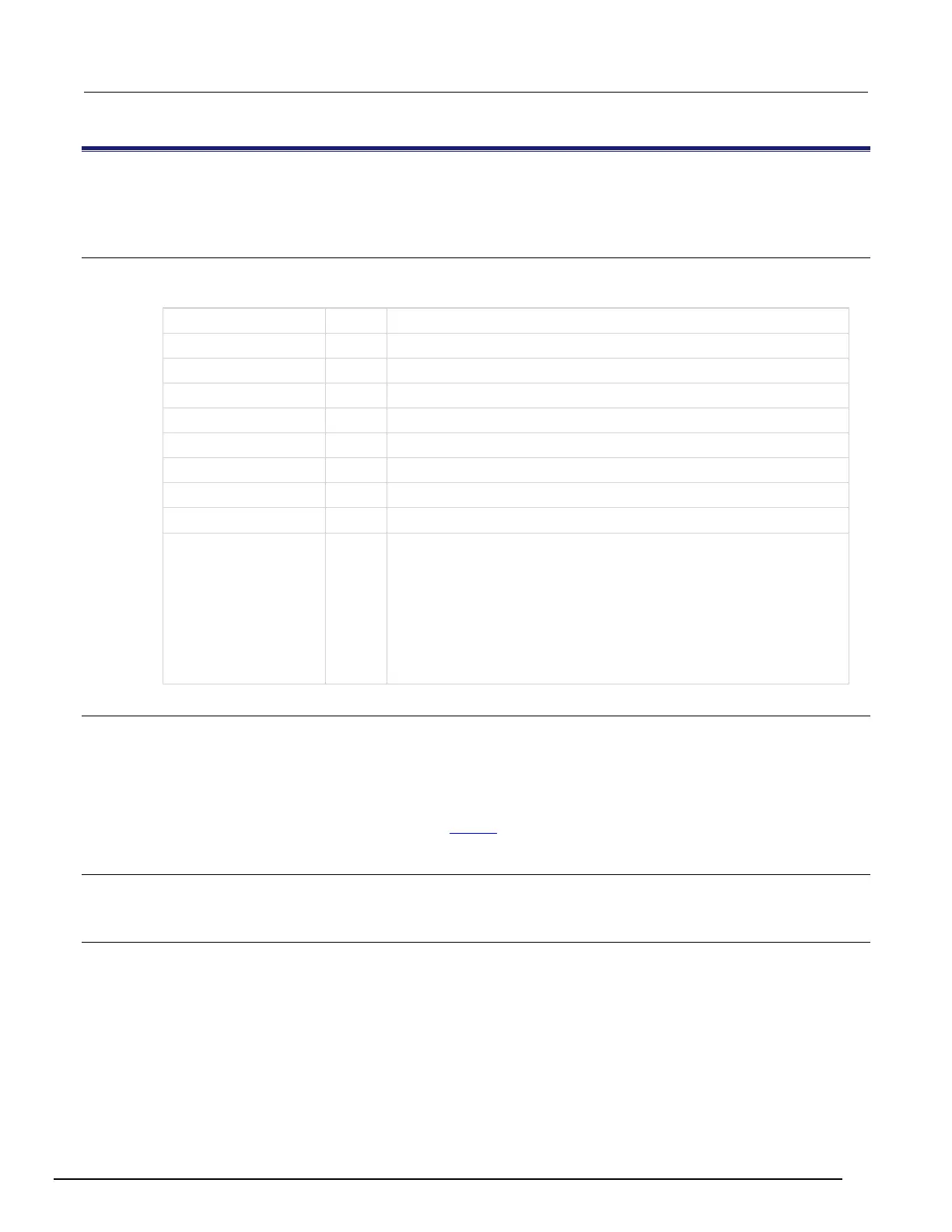

Usage

double beta2(int e, int b, int c, int sub, double ice, double vce, double *vbeout,

double *icout, char type);

The emitter pin of the device

The base pin of the device

The collector pin of the device

The substrate pin of the device

The targeted collector current, in amperes

The forced collector-emitter voltage, in volts

Type of transistor: "N" or "P"

The measured base voltage

The measured collector current

-1.0 = TYPE not "N" or "P"

-2.0 = SMU2 overload

-3.0 = Divide by 0, or < 0.01

-4.0 = > 10 K

-5.0 = Too many iterations

-6.0 = Emitter voltage limit reached; developed emitter voltage is

within 98 % of the 3 V voltage limit

Details

If a positive substrate pin is specified, the substrate is grounded. If a positive substrate pin is not

specified, the substrate is left floating.

A delay is incorporated into the beta2 subroutine; this delay is the calculated time required for stable

forcing of emitter current with a 3 V voltage limit.

A faster and simpler subroutine to use is beta2a (on page 3-4).

V/I polarities

The polarities of V

CE

and I

E

are determined by device type.

Source-measure units (SMUs)

SMU1: Forces I

E

, 3 V voltage limit

SMU2: Forces V

CE

, maximum current limit, measures I

CE

SMU3: Forces 0.0 V, measures base current (I

B

)

Loading...

Loading...