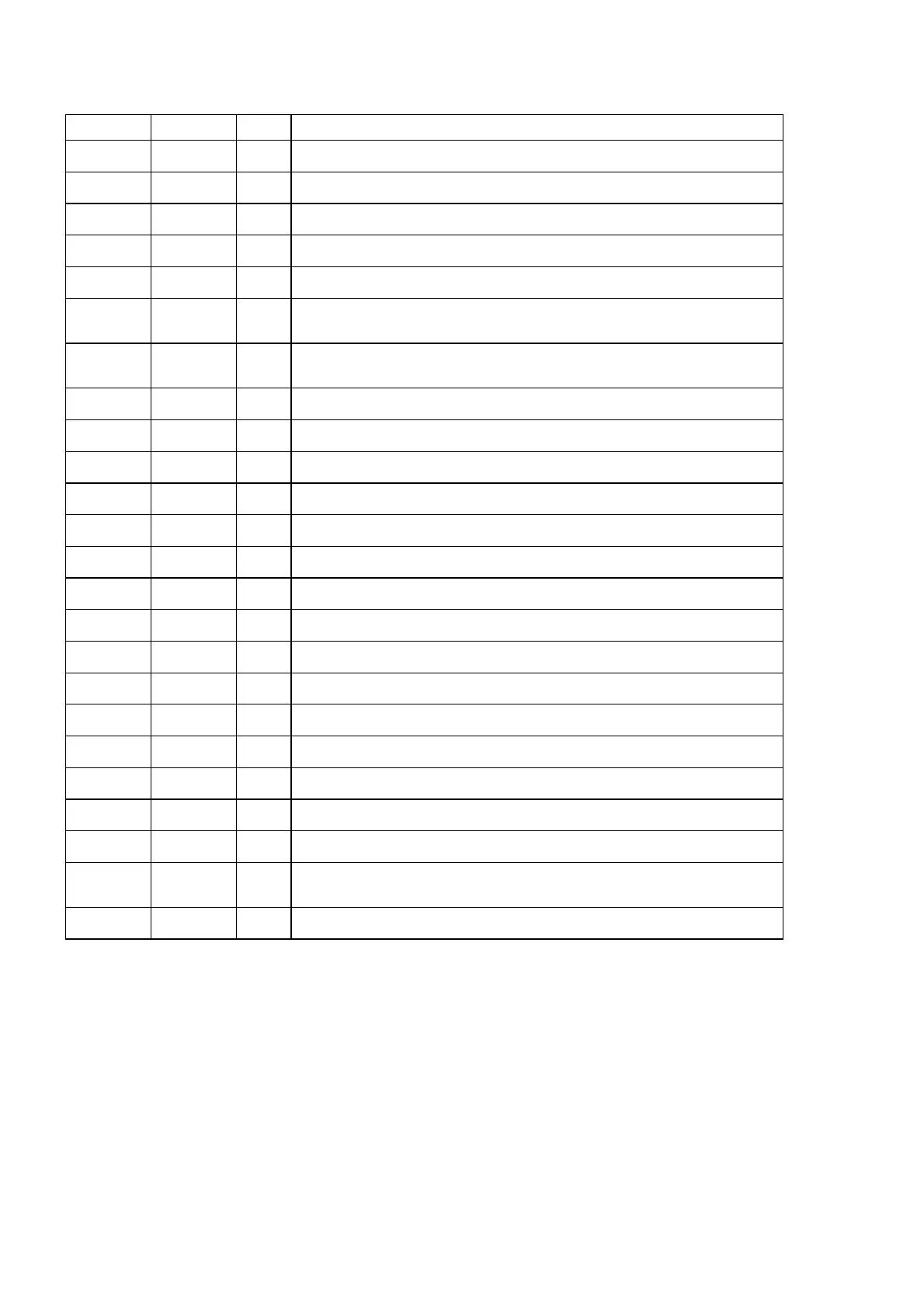

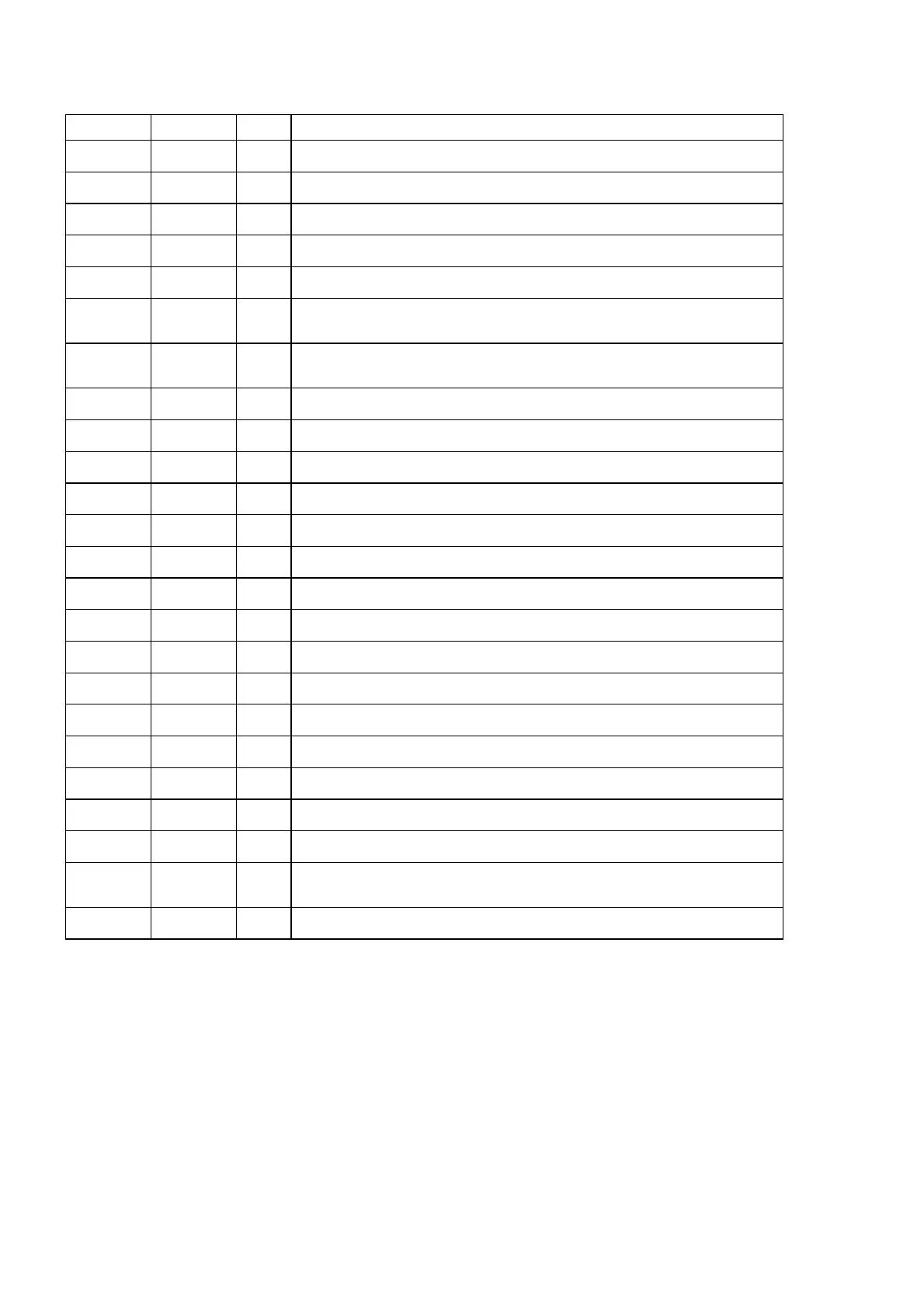

182

QF61 : SAA7115HL/V1/G

SYMBOL PIN I/O/P DESCRIPTION

V

DDE

1 P digital supply voltage 3.3 V (external pad supply)

TDO 2 O

Test Data Output for Boundary Scan Test

(2)

TDI 3 I

Test Data Input for Boundary Scan Test (with internal pull-up)

(2)

XTOUT 4 O crystal oscillator output signal, auxiliary signal

V

XSS

5P

ground pin for crystal oscillator

XTALO 6 O

24.576 (32.11) MHz crystal oscillator output; not connected if XTALI is driven

by an external single-ended oscillator.

XTALI 7 I

Input terminal for 24.576 (32.11) MHz crystal oscillator or connection of exter-

nal oscillator with TTL compatible square wave clock signal.

V

XDD

8P

supply voltage pin of crystal oscillator

V

SSA2

9P

ground for analog inputs AI2x

AI24 10 I

analog input 24

V

DDA2

11 P analog supply voltage for analog inputs AI2x (3.3V)

AI23 12 I

analog input 23

AI2D 13 I

differential input for ADC channel 2 (pins AI24, AI23, AI22, AI21)

AI22 14 I

analog input 22

V

SSA1

15 P

ground for analog inputs AI1x

AI21 16 I

analog input 21

V

DDA1

17 P

analog supply voltage for analog inputs AI1x (3.3V)

AI12 18 I

analog input 12

AI1D 19 I

differential input for ADC channel 1 (pins AI12, AI11)

AI11 20 I

analog input 11

AGND 21 P analog ground connection

AOUT 22 O

Analog test output (do not connect)

V

DDA0

23 P

analog positive supply voltage for both internal CGC (Clock Generation Cir-

cuit) (3.3V)

V

SSA0

24 P

analog ground for internal CGC

Loading...

Loading...