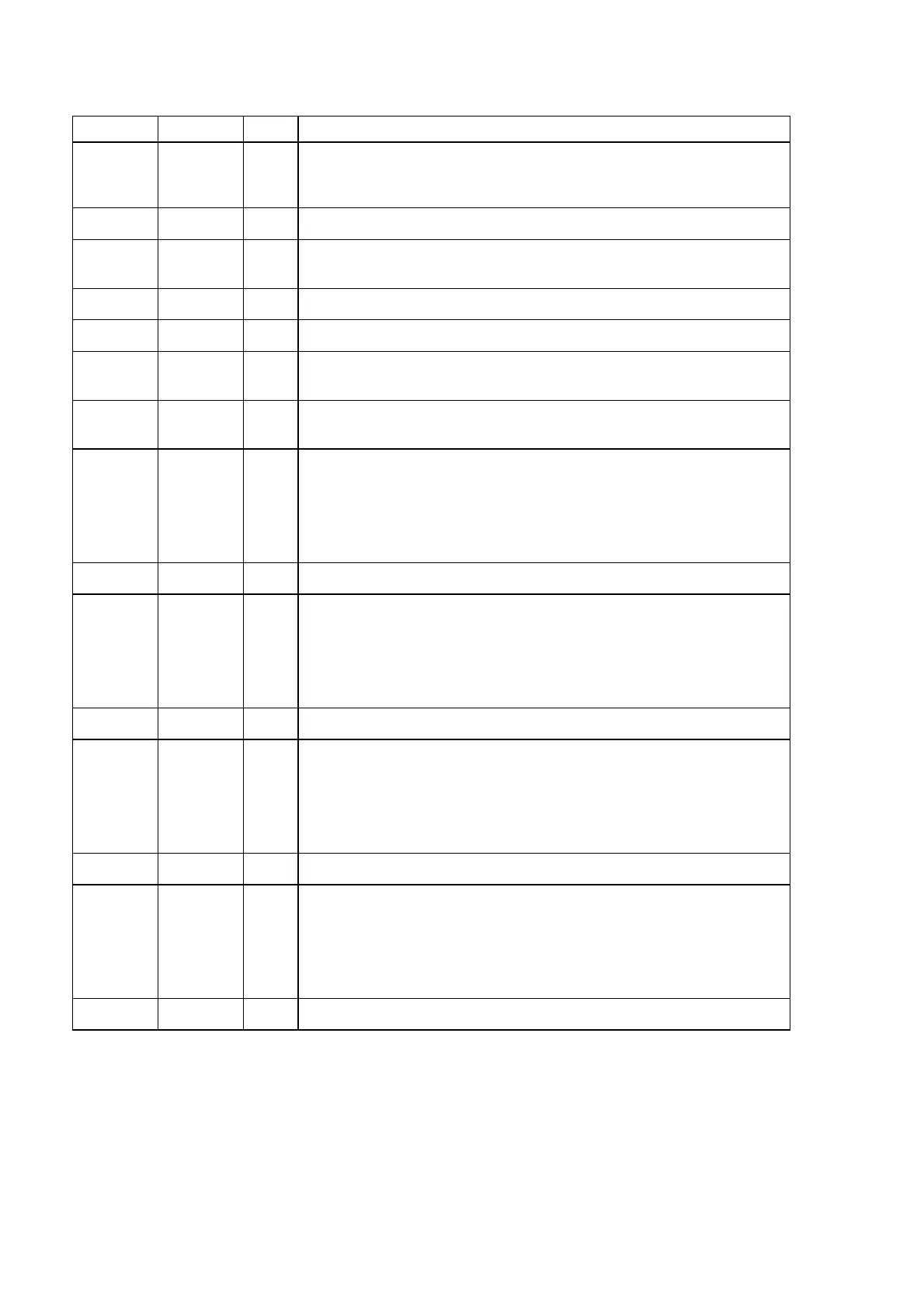

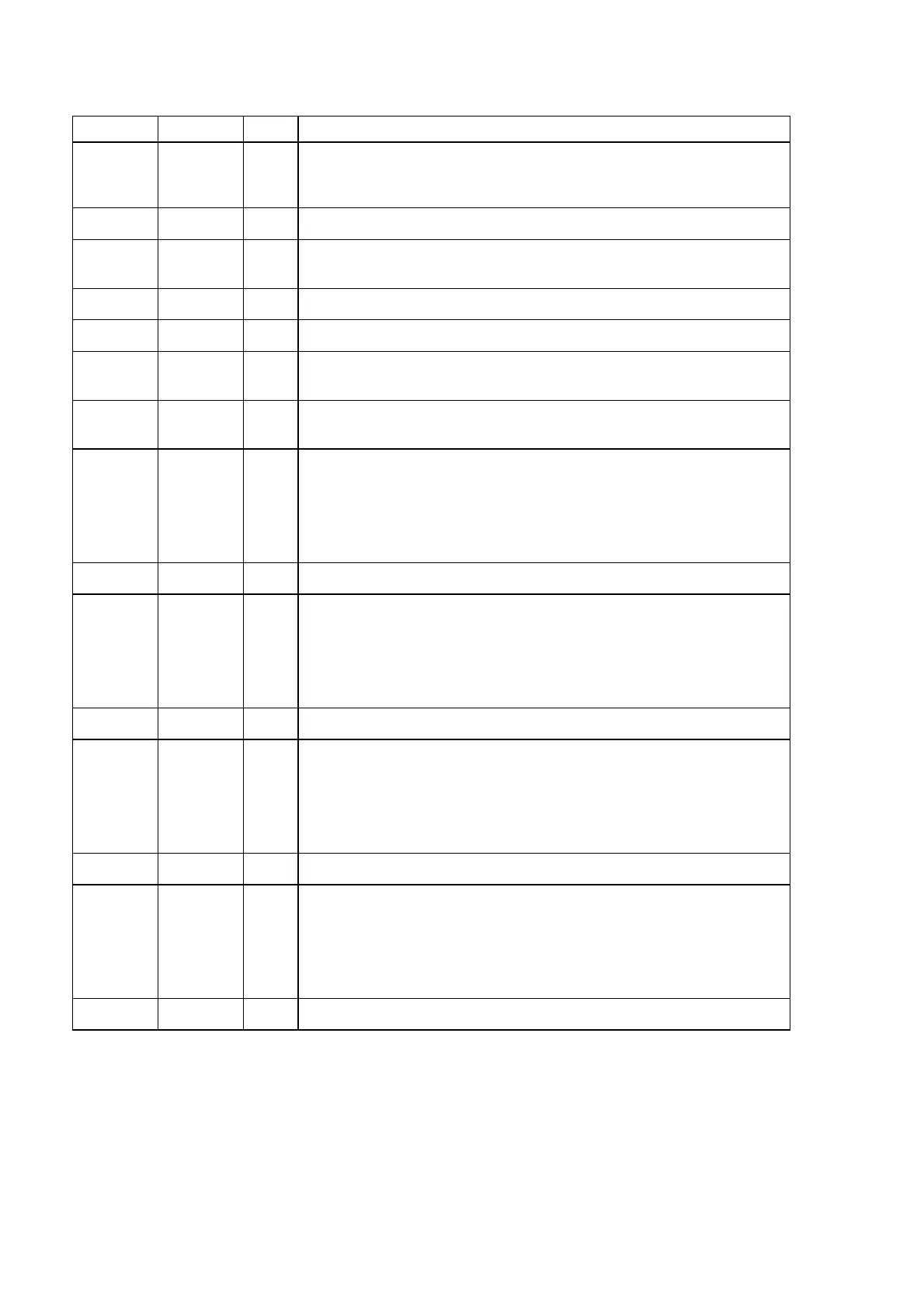

184

QF61 : SAA7115HL/V1/G

ITRI 47 I (/O)

image-port output control signal, effects all I-port pins incl. ICLK,

enable and active polarity is under software control (bits IPE in subaddr. “87”)

output path used for Testing: scan output

IGP0 48 O general purpose output signal 0; image-port (controlled by subaddr. “84”,”85”)

IGP1 49 O

general purpose output signal 1; image-port (controlled by subaddr. “84”,”85”),

same functions as IGP0

V

SSE

50 P digital ground (external pad supply)

V

DDE

51 P digital supply voltage 3.3 V (external pad supply)

IGPV 52 O

multi purpose vertical reference output signal; image-port

(controlled by subaddr. “84”,”85”)

IGPH 53 O

multi purpose horizontal reference output signal; image-port

(controlled by subaddr. “84”,”85”)

IPD7

IPD6

IPD5

IPD4

54

55

56

57

O

O

O

O

image port data output

V

DDI

58 P digital supply voltage 3.3 V (internal core supply)

IPD3

IPD2

IPD1

IPD0

59

60

61

62

O

O

O

O

image port data output

V

SSI

63 P digital ground (internal core supply)

HPD7

HPD6

HPD5

HPD4

64

65

66

67

I/O

I/O

I/O

I/O

Host port data I/O, carries UV chrominance information in 16 bit video I/O

modes

V

DDI

68 P digital supply voltage 3.3 V (internal core supply)

HPD3

HPD2

HPD1

HPD0

69

70

71

72

I/O

I/O

I/O

I/O

Host port data I/O, carries UV chrominance information in 16 bit video I/O

modes

TEST1 73 I do not connect, reserved for future extensions and for Testing: scan input

SYMBOL PIN I/O/P DESCRIPTION

Loading...

Loading...