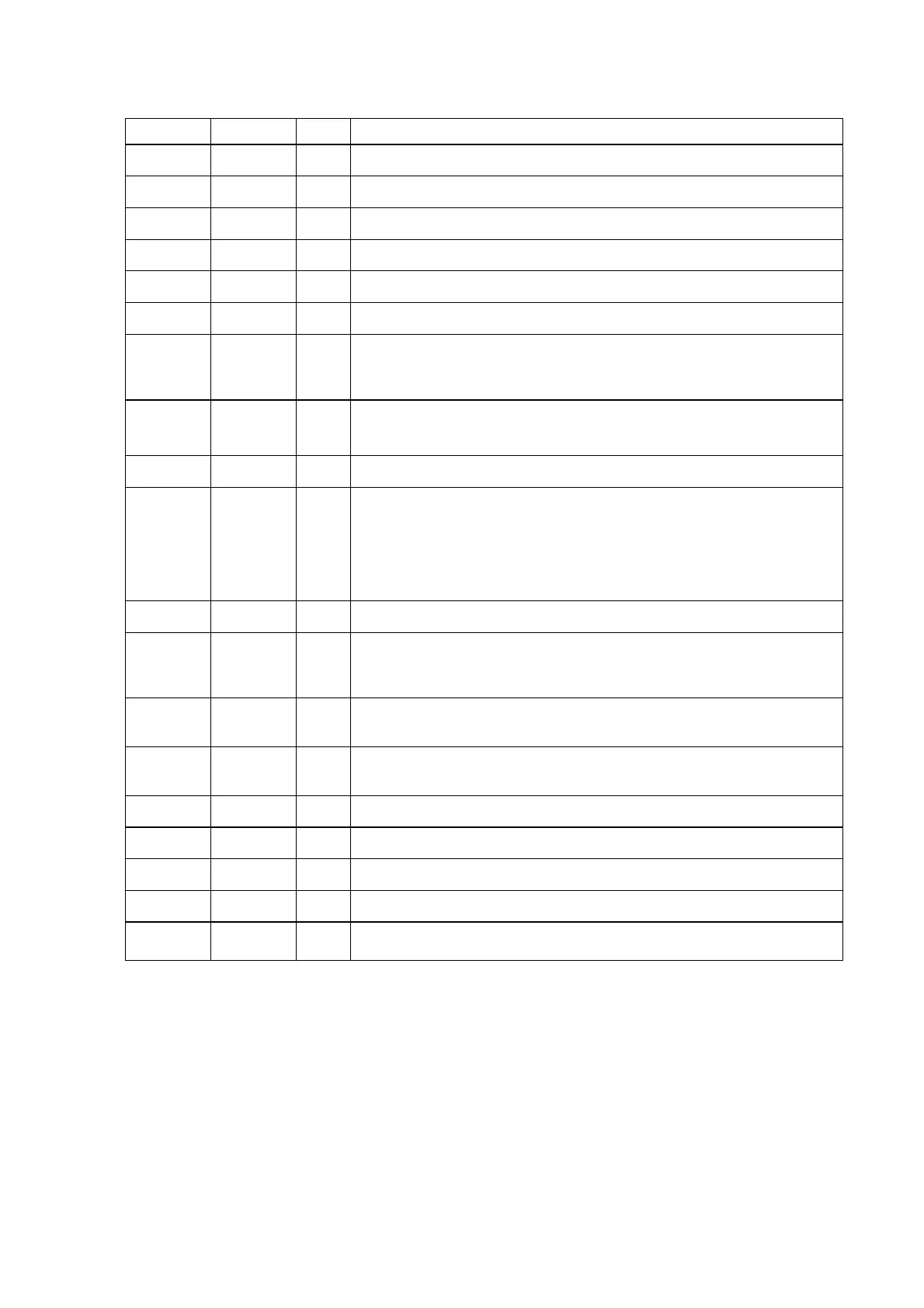

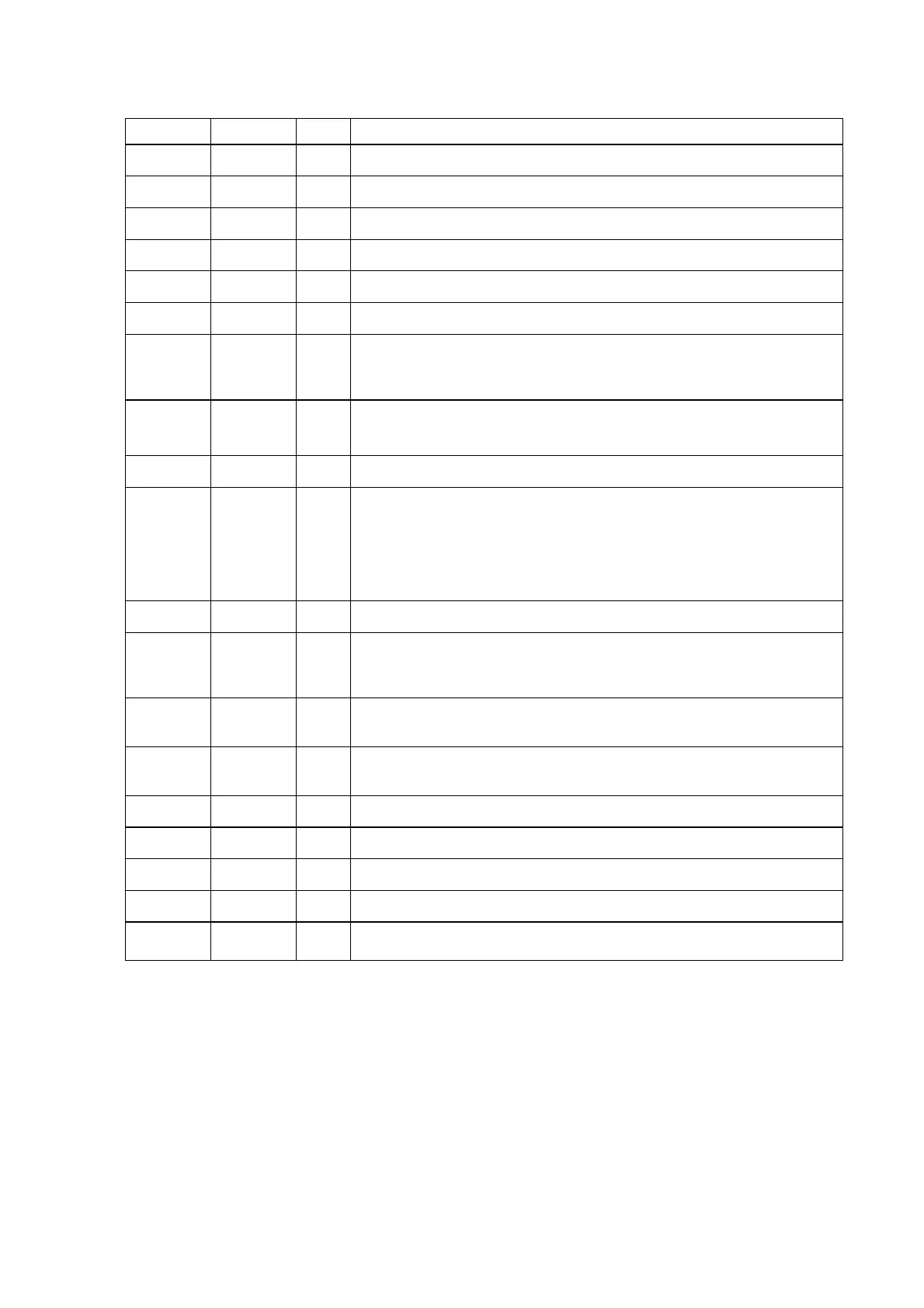

185

QF61 : SAA7115HL/V1/G

TEST2 74 I do not connect, reserved for future extensions and for Testing: scan input

V

DDE

75 P digital supply voltage 3.3 V (external pad supply)

V

SSE

76 P digital ground (external pad supply)

TEST3 77 I do not connect, reserved for future extensions and for Testing: scan input

TEST4 78 O do not connect, reserved for future extensions and for Testing: scan output

TEST5 79 I do not connect, reserved for future extensions and for Testing: scan input

XTRI 80 I

X-port output control signal, effects all X-port pins (XPD[7:0], XRH, XRV, XDQ

and XCLK)

enable and active polarity is under software control (bits XPE in subaddr. “83”)

XPD7

XPD6

81

82

I/O

I/O

expansion-port data:

In eight bit video output mode: these signal represent the video bits 7 to 6.

In ten bit video output mode: these signal represent the video bits 9 to 8.

V

DDI

83 P digital supply voltage 3.3 V (internal core supply)

XPD5

XPD4

XPD3

XPD2

84

85

86

87

I/O

I/O

I/O

I/O

expansion-port data:

In eight bit video output mode: these signal represent the video bits 5 to 2.

In ten bit video output mode: these signal represent the video bits 7 to 4.

V

SSI

88 P digital ground (internal core supply)

XPD1

XPD0

89

90

I/O

I/O

expansion-port data:

In eight bit video output mode: these signal represent the video bits 1 to 0.

In ten bit video output mode: these signal represent the video bits 3 to 2.

XRV 91 I/O

vertical reference I/O expansion-port:

In ten bit video output mode: this signal represents the video bit 0.

XRH 92 I/O

horizontal reference I/O expansion-port:

In ten bit video output mode: this signal represents the video bit 1.

V

DDI

93 P digital supply voltage 3.3 V (internal core supply)

XCLK 94 I/O clock I/O expansion port

XDQ 95 I/O data qualifier I/O expansion port

XRDY 96 O task flag or read signal from scaler, controlled by XRQT (subaddr. 83H)

TRSTN 97 I

Test ReSeT Not for Boundary Scan Test (with internal pull-up); for board design

without Boundary Scan connect TRSTN to ‘ground’

(1)

SYMBOL PIN I/O/P DESCRIPTION

Loading...

Loading...