186

QF61 : SAA7115HL/V1/G

Notes

1. This pin provides easy initialization of BST circuitry. TRSTN can be used to force the TAP (Test Access Port)

controller to the Test-Logic-Reset state (normal operation) at once

2. According to the IEEE1149.b1-1994 standard the pads TDI and TMS are input pads with a internal pull-up transistor

and TDO a tri-state output pad. TCK, TRSTN are also build with internal pull_up

TCK 98 I

Test Clock for Boundary Scan Test (with internal pull-up)

(2)

TMS 99 I

Test Mode Select for Boundary Scan Test or Scan Test (with internal pull-up)

(2)

V

SSE

100 P digital ground (external pad supply)

SYMBOL PIN I/O/P DESCRIPTION

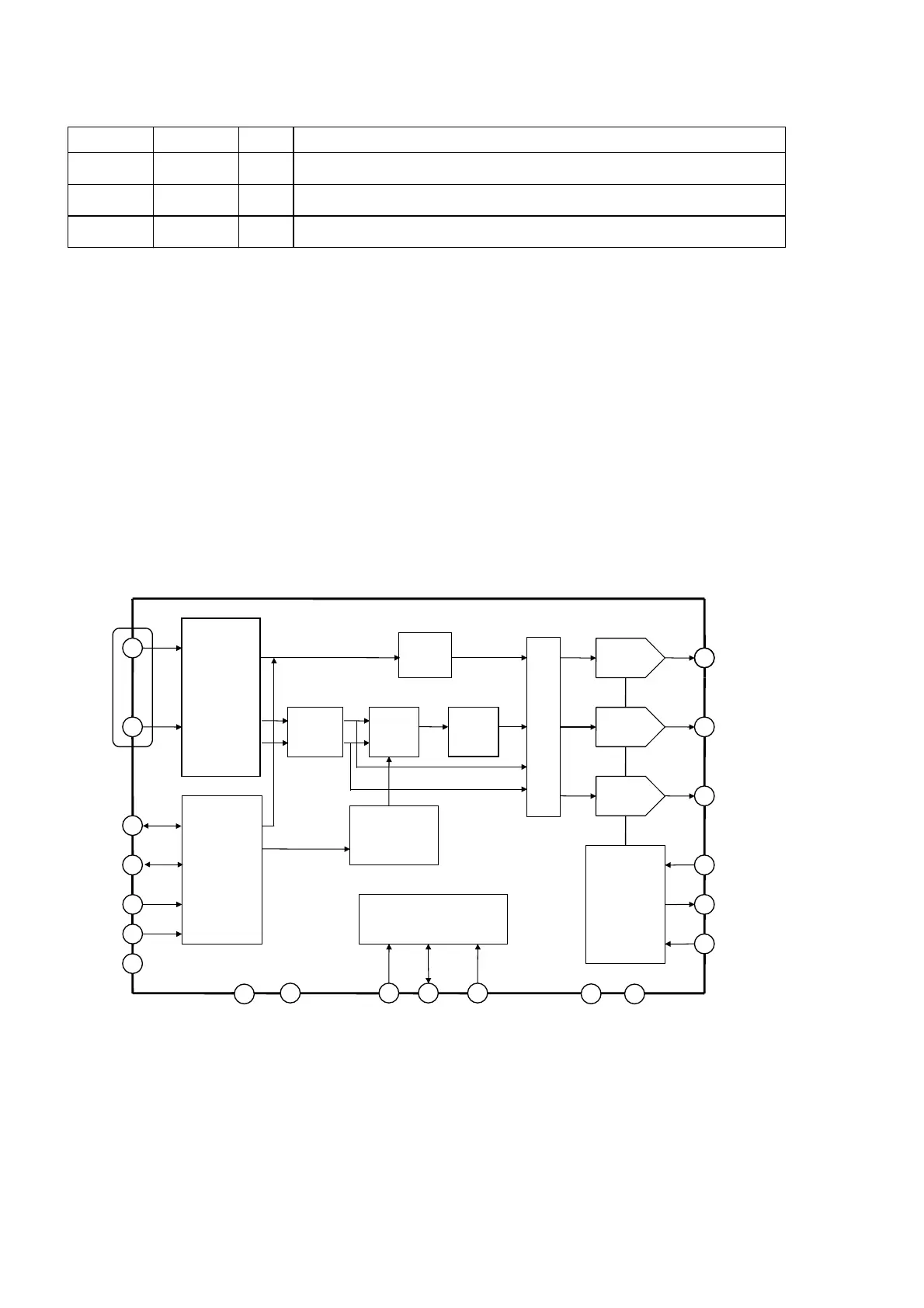

QF62 : AK8812P

x2

LPF-

Luma

x2

LPF-

Chroma-2

Sub Carrier

Run in Clock

Video timing

&

Base Wave

Generator

I

2

C

Interface

U,V

MOD

VREF

SCL SDA

10-bit

DAC

YCbCr (4:2:2)

To

YUV (4:4:4)

10-bit

DAC

10-bit

DAC

LPF

Chroma-1

REFIN

REFOUT

IREF

/RESET

DVDD

FID/VSYNC

HSYNC

SYSCLK

DATA

D7 - D0

SELA

COMPOSITE / U

Y

CHROMA / V

SYSINV

Selector

AVDD AVSSDVSS

Loading...

Loading...