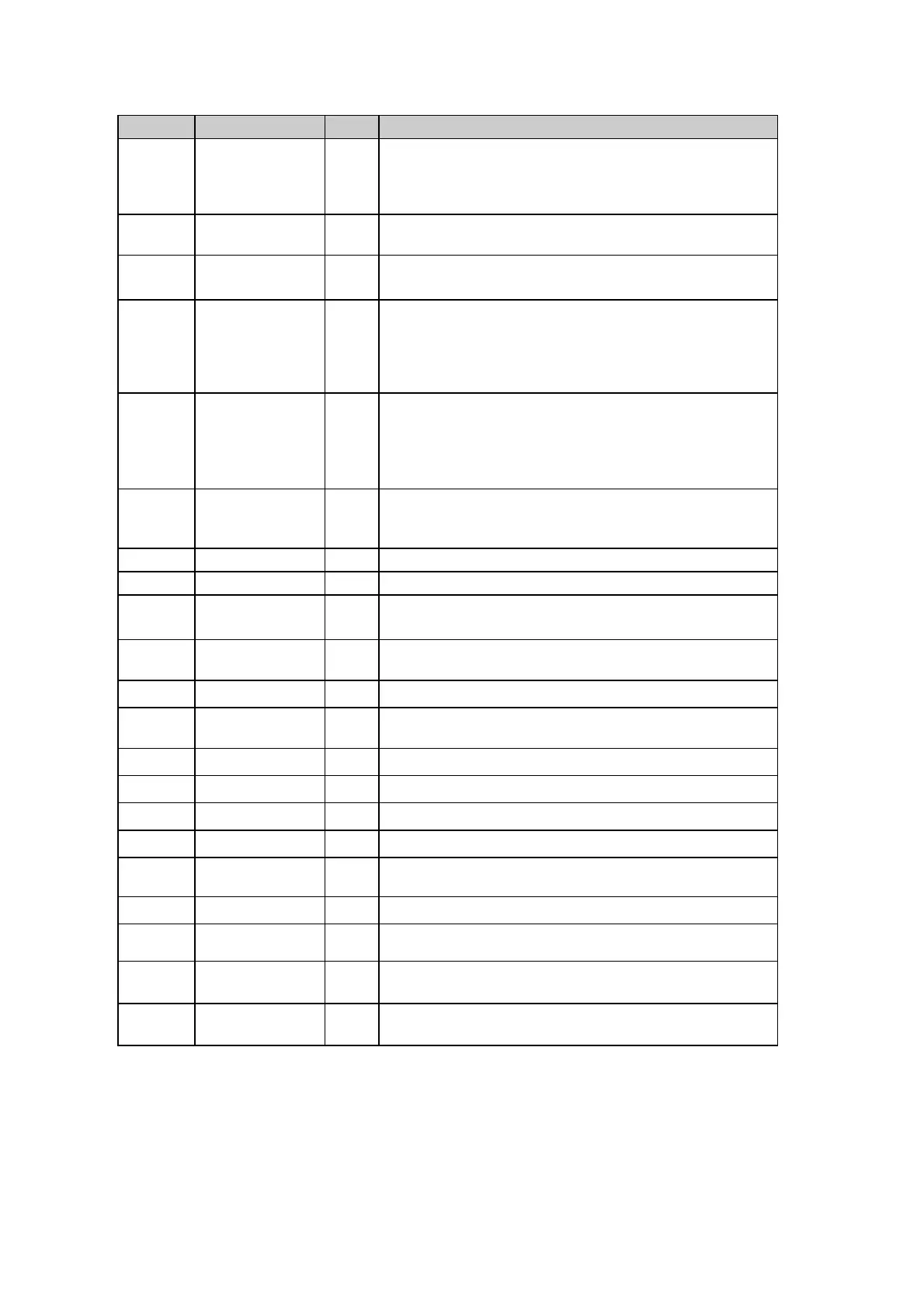

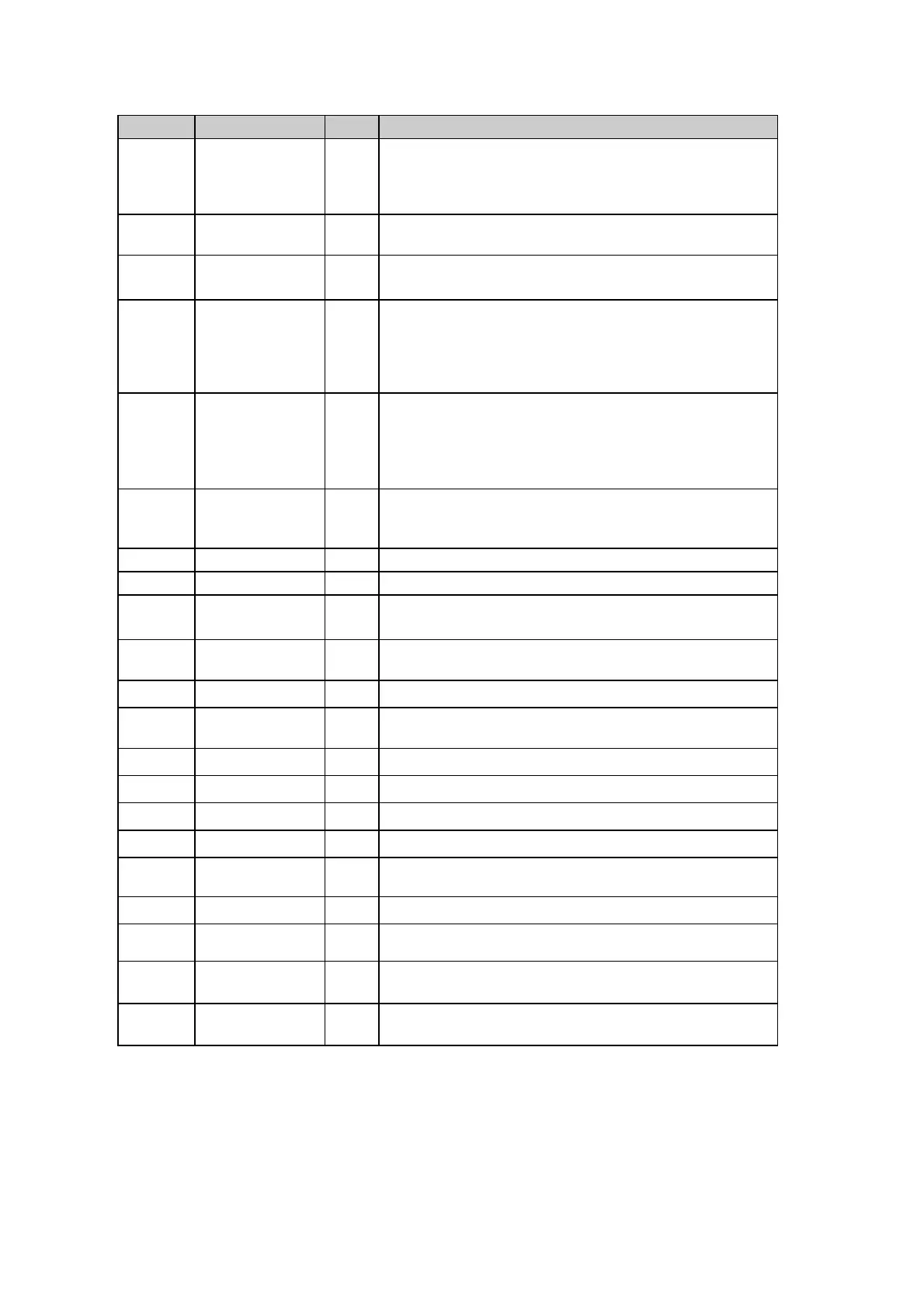

187

QF62 : AK8812P

No. Pin Name I/O Description

2-5,

8-11

D7 - D0

I

27MHz 8-Bit 4:2:2 multiplexed Y,Cb,Cr Data Input.

For Rec.656 format, AK8811/12 decodes EAV.

For non-Rec.656 format (without EAV), AK8811/12

operates in Master or Slave mode.

41 SYSCLK

I

27MHz Clock Input. The polarity could be inverted by

SYSINV.

48 SYSINV

I

“L “ : data is latched with rising edge.

“H” : data is latched with falling edge.

18 /RESET

I After this pin becomes “L”, AK8811/12 starts the

internal initializing sequence.

After initializing sequence, AK8811/12 is set NTSC

mode, Rec.656 decoding mode. All DACs Off

condition.

45

FID

/VSYNC

I/O Either of FID or VSYNC selected by the register.

Rec.656 decode mode :Output

Master mode : Output

Slave mode : Input

FID shows that “L” is odd field and ”H” is even field.

46 HSYNC

I/O Rec.656 decode mode : Output

Master mode : Output

Slave mode : Input

15 SCL I Serial interface clock

16

SDA I/O Serial interface data

14 SELA

I The slave address is set with this pin.

“L”:40H “H”:42H

27 VREFOUT

O Output of the Internal Vref. Terminate with 0.1uF or

more capacitor.

28

VREFIN

I

Input of the Reference Voltage

29 IREF

O

The currents flow this pin adjusts the full-scale

output current of the DAC.

24 COMPOSITE/U

O

Output of Composite Video signal or component U

22 CHROMA/V

O

Output of the C signal or component V

20 Y O Output of Luminance Signal.

21,26 AVDD P Analog +3.3V

6,31,

42,44

DVDD P Digital +3.3V

19,23,25

AVSS G Analog Ground

7,17,47,

40,30

DVSS G Digital Ground

12,13

TEST1

TEST2

I

Test pin. Ground for normal operation

1, 32-

39,43

PD[9:0]

I/O

Test pin. Open for normal operation

Loading...

Loading...