Theory of Operation: Controller 3-35

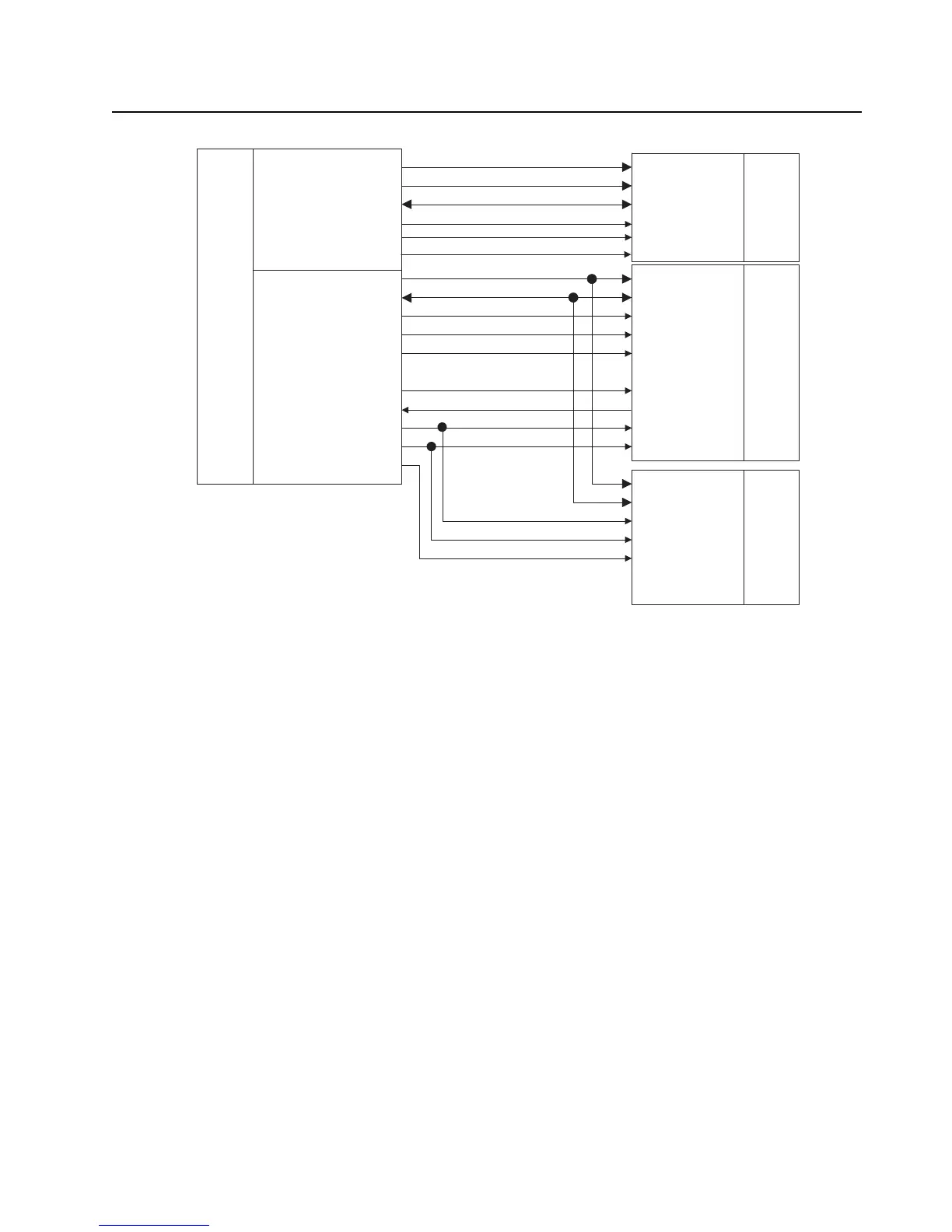

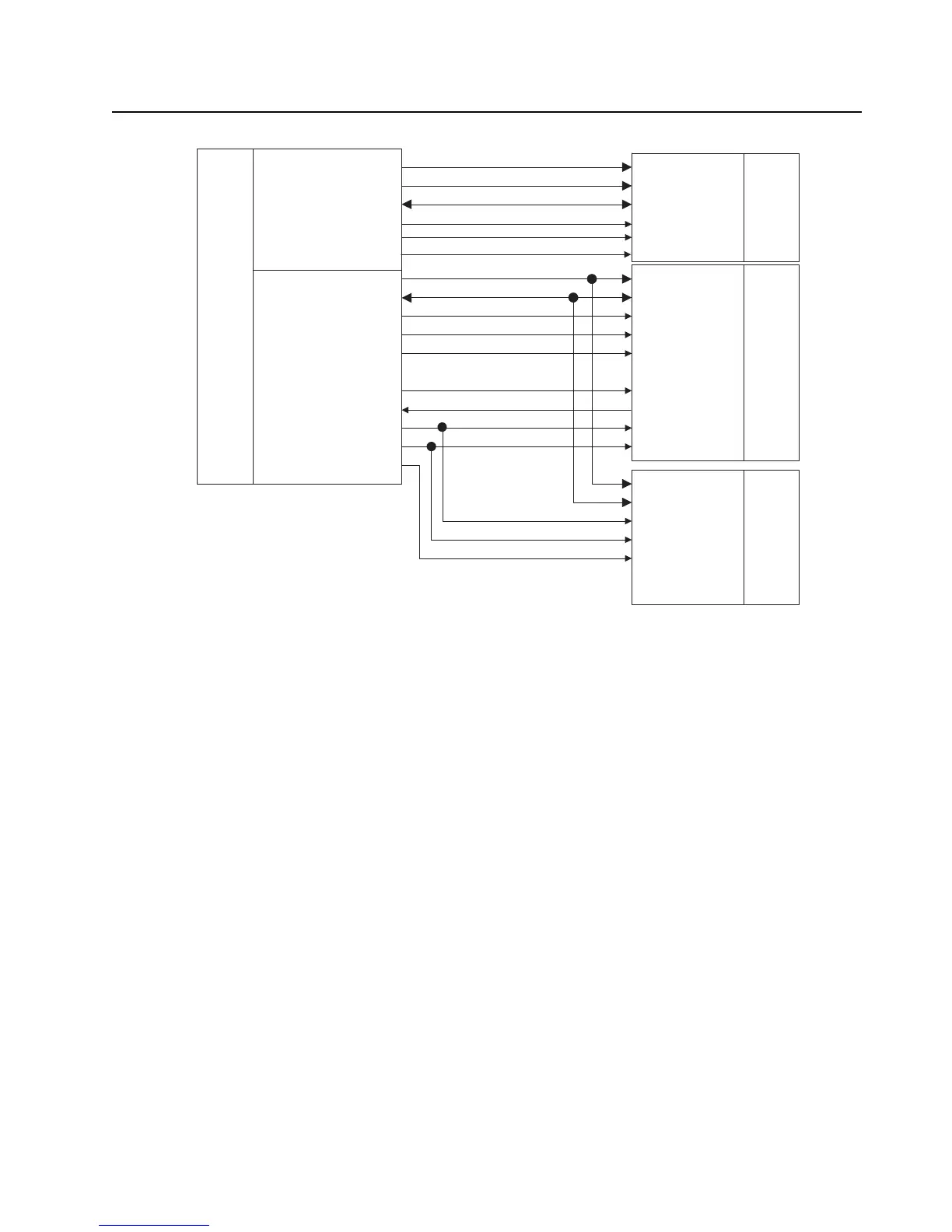

Figure 3-25. OMAP Memory Interface

3.2.4.3 Asynchronous External Memory Interface

The EMIFS is used for transferring data between the ARM or DSP cores and the 64 MB External

NOR Flash memory (U6304). The Flash memory is a non-volatile memory unit, primarily used to

store the radio's executable code, along with device configuration values, event logs, and

initialization codes. The flash memory is primarily accessed during the main board’s power up and

power down cycles.

3.2.4.4 Flash Memory (6304)

The Flash memory located in close proximity to the OMAP processor is a 64 MB Numonyx 65nm

StrataFlash. The flash interface uses 16 data bits and 25 address bits. The flash IC is enabled by

OMAP processor's CS3 line. The flash IC also features a WAIT line that is capable of halting data

flow between the processor and flash IC while operating in synchronous read mode.

3.2.4.5 CPLD Interface (U6101)

The CPLD (U6101) registers are also mapped to the Asynchronous External Memory Interface.

These registers control the CPLD GPIO pins and enable the OMAP to expand its GPIO capability via

memory mapped IO.

3.2.4.6 Synchronous External Memory Interface

This interfaces the OMAP to a 32 MB Double Data Rate (DDR) RAM IC (U6301). Upon boot-up

OMAP configures this interface to operate in synchronous mode at 96 MHz. This volatile memory

unit is primarily accessed during code execution.

SDATA_15:0

SADD_13:0

DDR_CTRL_5:0

SDCLK

SDCLKX

FADD_25:1

FDATA_15:0

NF_ADV

NF_CS1

NF_CS3

NF_OE

NF_WE

FCLK

NF_RP

FRDY

EMIFF

EMIFS

OMAP

DDR

SDRAM

DDR_CTRL_5:0

A13:0

DQ15:0

CK

CK#

EN_CLKE

A25:1

DQ15:0

EN_CE

EN_RST

EN_WE

CLK

WAIT

ADV

EN_WE

ADDR_5:1

DATA_4:0

CPLD_ADV

CPLD_R/W

CPLD_CS

FLASH MEMORY

CPLD

WAIT_SW_EN

SDCLK_EN

Loading...

Loading...