2–28

Principles of Operation

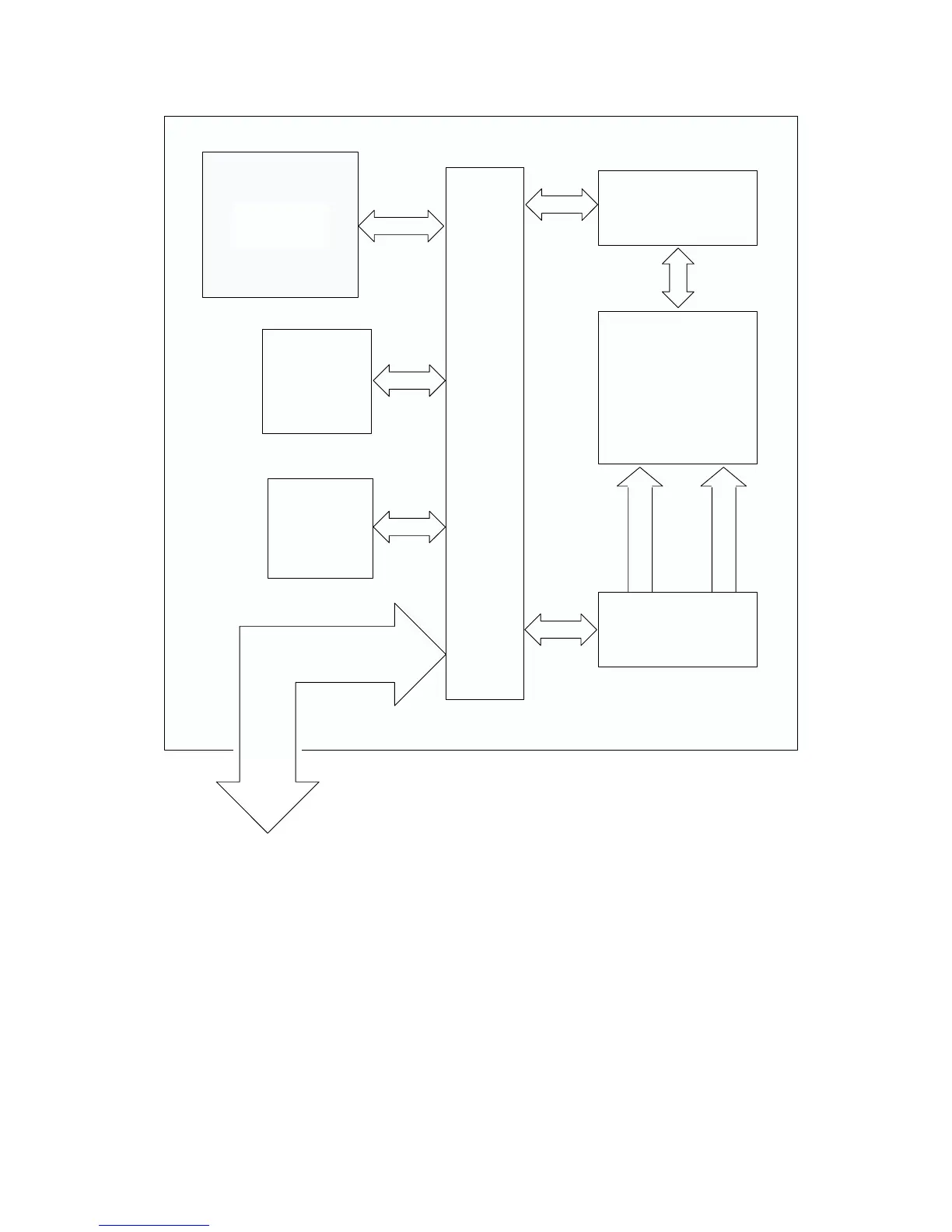

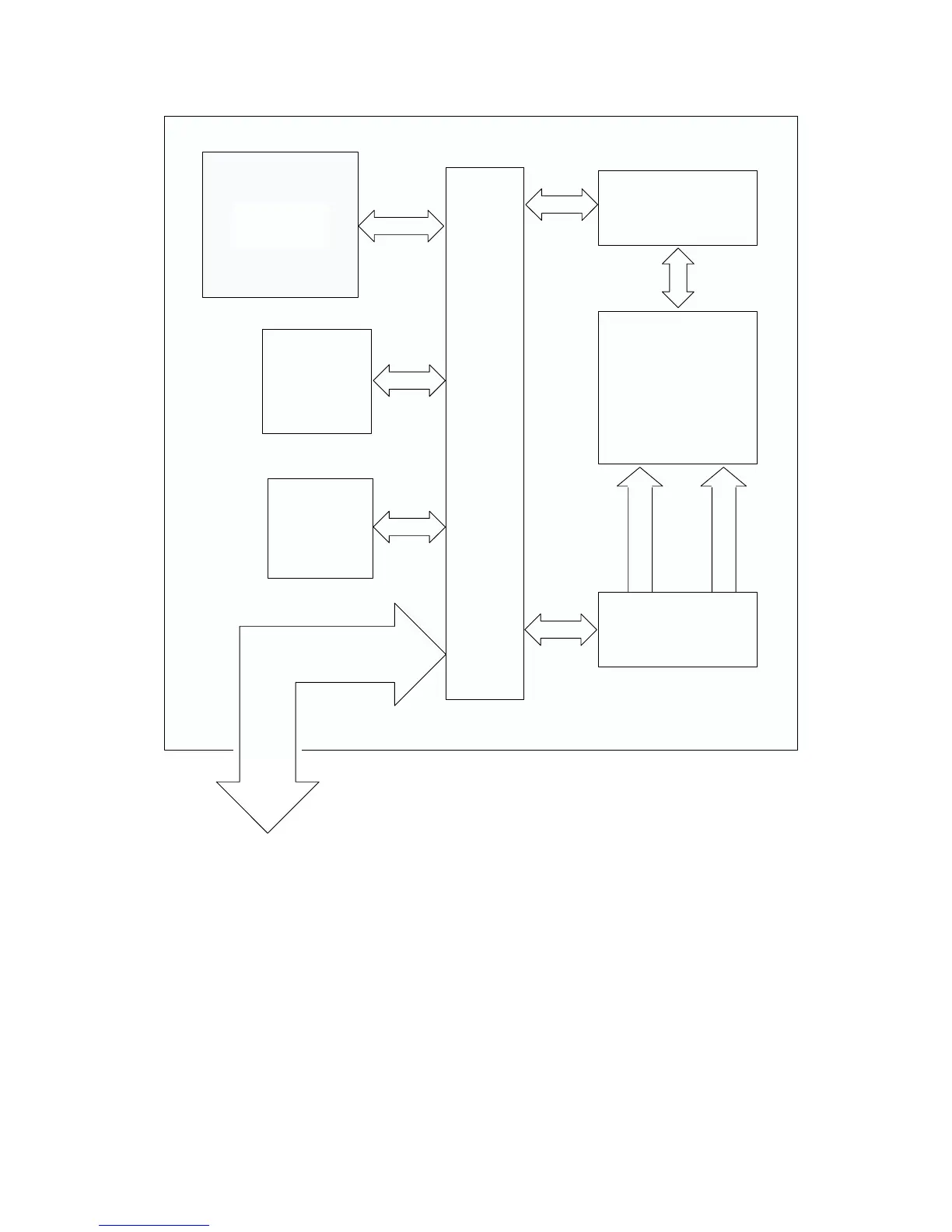

68EC030

CPU

68EC030 BUS

16 Bit Port

25 Bit Address

FPU

68882

27256

Boot ROM

32K Byte

8 Bit Port

LMI 030 Board

DRAM

4 Banks of

1M/4M Byte

32 Bit Port

DRAM

Controller

Row/Col Address

RAS CAS WE OE*

84C31

Data

Buffers

74F245

LMI Board

* RAS = Row Address Strobe

CAS = Column Address Strobe

WE = Write Enable

OE = Output Enable

Figure 2–17. Hardware Implementation of the LMI 030 Board

Communicating with the Host Computer

The Z8S180 processor runs both the parallel and serial interfaces.

Host Parallel Input Parallel inputs are nine bits wide, but the Z8S180 direct

memory access (DMA) used to make the transfer is only eight bits. The

Loading...

Loading...