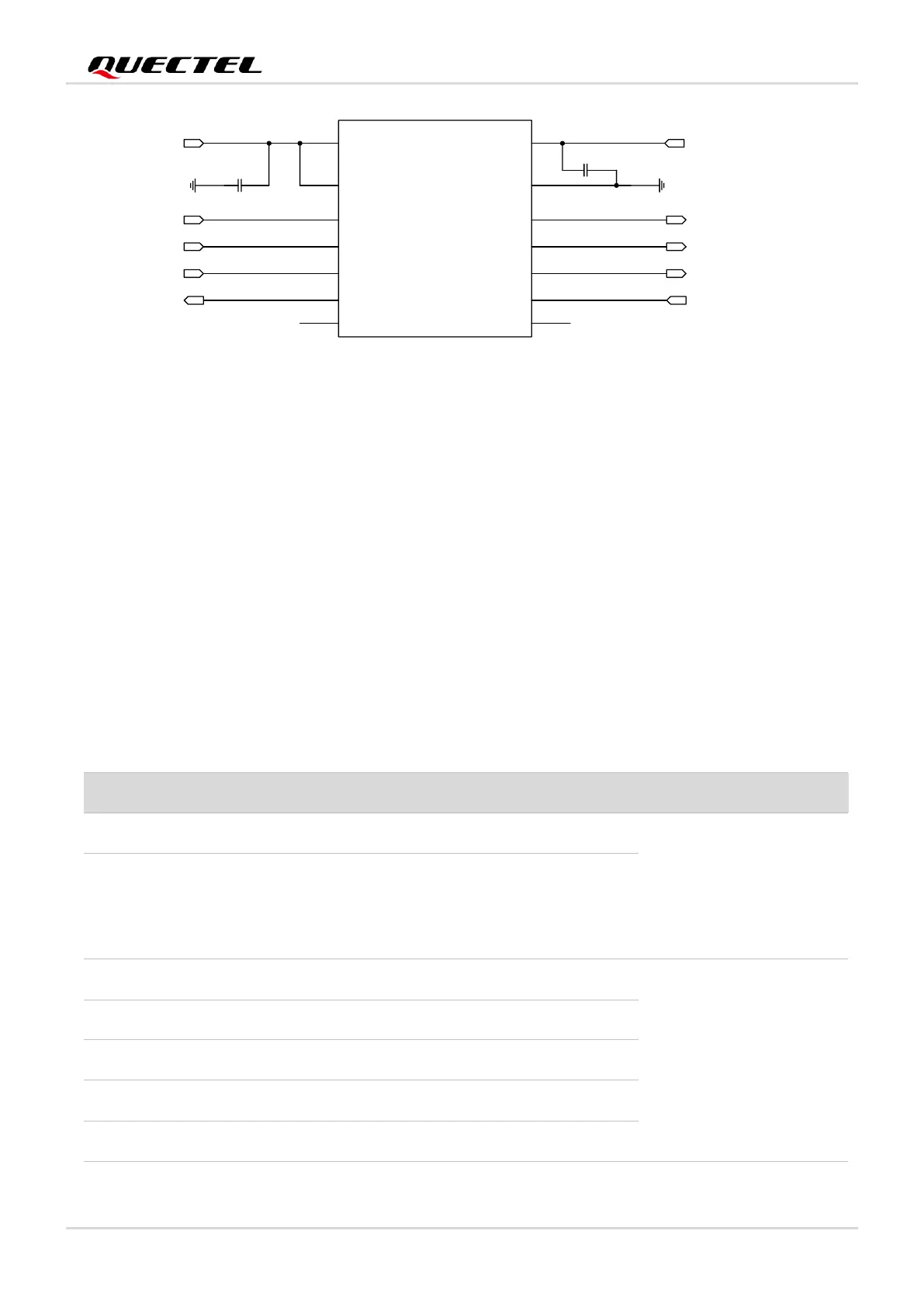

Figure 31: Reference Circuit of SPI with a Voltage-level Translator

4.11. PCIe Interface

The module provides one integrated PCIe (Peripheral Component Interconnect Express) interface. The

key features of the PCIe interface are mentioned below:

⚫ PCI Express Specification Revision 3.0 compliance.

⚫ Data rate at 8 Gbps per lane for PCIe 3.0.

⚫ Used to connect to an external Ethernet IC (MAC and PHY) or Wi-Fi IC.

Table 26: Pin Definition of PCIe Interface

In root complex mode, it is

an output signal.

In endpoint mode, it is an

input signal. Requires

differential impedance of

85 Ω.

Loading...

Loading...