Bit 5 MSCE: Mask for transmission errors on the Safe Channel

1 = A transmission error on the Safe Channel sets the interrupt signal.

0 = A transmission error on the Safe Channel does not set the interrupt signal.

Bit 4 Not implemented: Read as "0".

Bit 3 MPOS: Mask for fast position error

1 = An error in the fast position sets the interrupt signal.

0 = An error in the fast position does not set the interrupt signal.

Bit 2 MVPOS: Mask for safe position error

1 = An error in the safe position sets the interrupt signal.

0 = An error in the safe position does not set the interrupt signal.

Bit 1 MDTE: Mask for estimator deviation threshold error warning

1 = A high estimator deviation threshold error sets the interrupt signal.

0 = A high deviation threshold error value does not set the interrupt signal.

Bit 0 MPRST: Mask for protocol reset warning

1 = A protocol reset sets the interrupt signal.

0 = A protocol reset does not set the interrupt signal.

Register 07h: Low Byte event mask

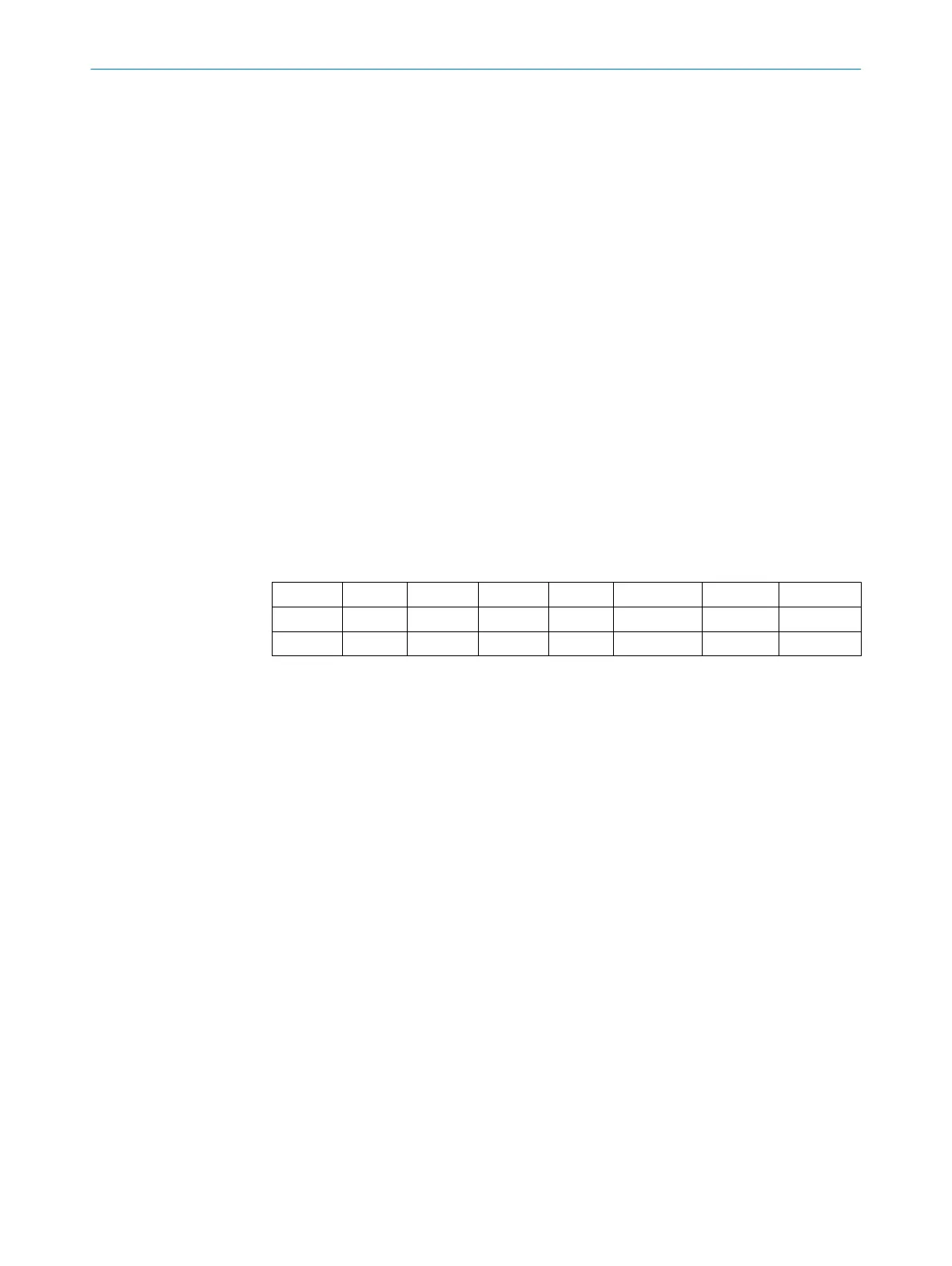

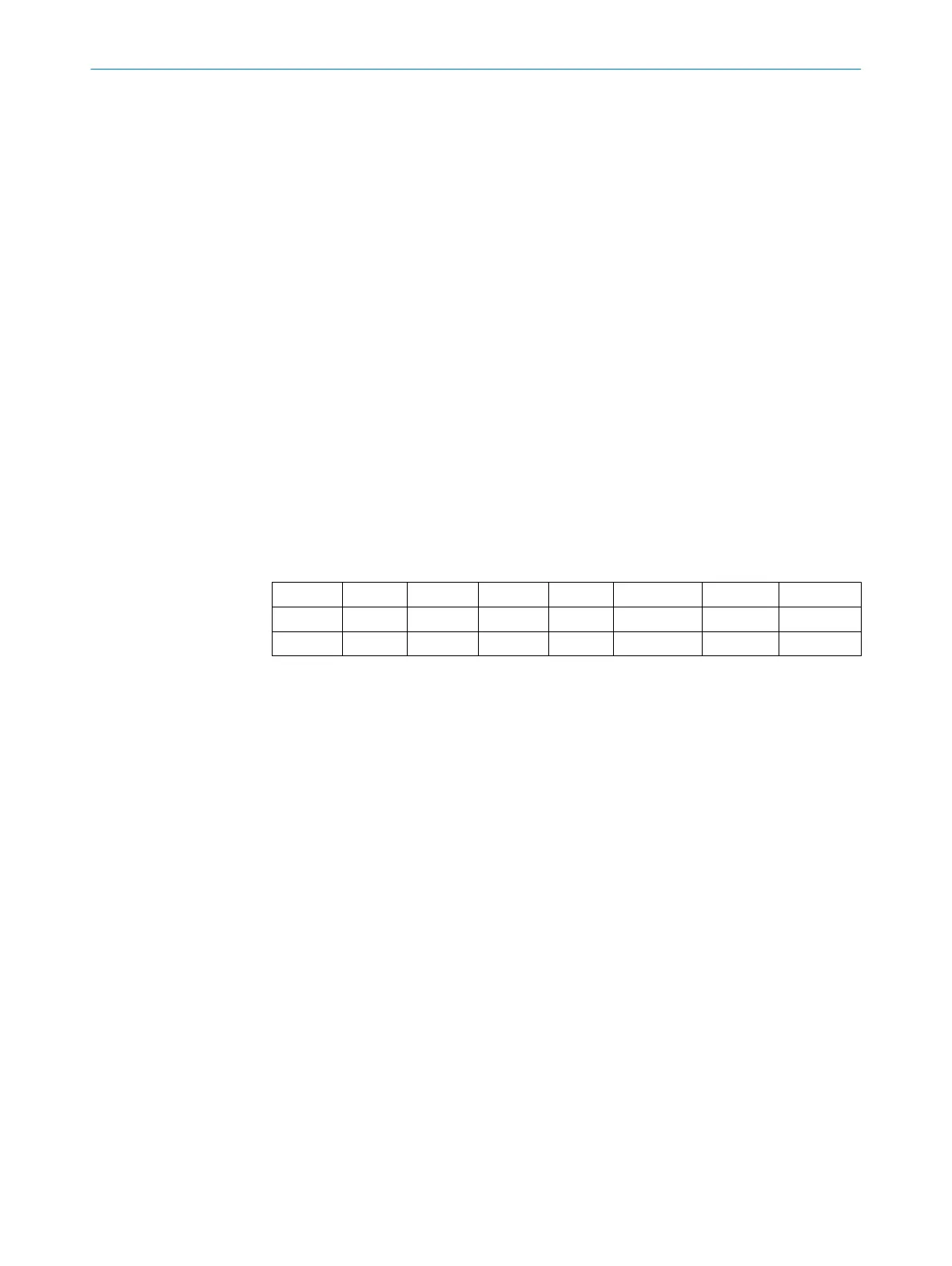

X-0 X-0 W-0 W-0 X-0 W-0 W-0 X-0

MMIN MANS MQMLW MFREL

Bit 7 Bit 0

Bit 7-6 Not implemented: Read as "0".

Bit 5 MMIN: Mask for message initialization confirmation

1 = The acknowledgment for the initialization of a DSL Slave message sets the inter-

rupt signal.

0 = The acknowledgment for the initialization of a DSL Slave message does not set the

interrupt signal.

Bit 4 MANS: Mask for erroneous answer to long message

1 = A transmission error during the answer to a long message sets the interrupt sig‐

nal.

0 = A transmission error during the answer to a long message does not set the inter-

rupt signal.

Bit 3

Not implemented: Read as "0".

Bit 2

MQMLW: Mask for low quality monitoring value warning

1 = A low quality monitoring value (see registers 03h and 05h) sets the interrupt

signal.

0 = A low quality monitoring value does not set the interrupt signal

Bit 1 MFREL: Mask for "channel free for "long message"'

1 = If a "long message" can be sent on the Parameters Channel, the interrupt signal

is set.

0 = If a "long message" can be sent on the Parameters Channel, the interrupt signal

is not set.

6

REGISTER MAP

40

T E C H N I C A L I N F O R M A T I O N | HIPERFACE DSL

®

8017595/ZTW6/2018-01-15 | SICK

Subject to change without notice

Loading...

Loading...