Bit 0 MFRES: Mask for "channel free for "short message"'

1 = If a "short message" can be sent on the Parameters Channel, the interrupt signal

is set.

0 = If a "short message" can be sent on the Parameters Channel, the interrupt signal

is not set.

6.3.6 Summary mask

In the MASK_SUM summary mask register, the DSL Slave collective events are deter‐

mined with which the SUM event monitoring in the event register as well as the signal to

the interrupt pin are set (interrupt).

Several events can be masked to trigger an interrupt. In addition, events from the DSL

Master can be combined with these events (see chapter 6.3.4).

NOTE

It should be noted that the MSUM bit from the MASK_H register is an OR connection of

all bits of the summary mask register.

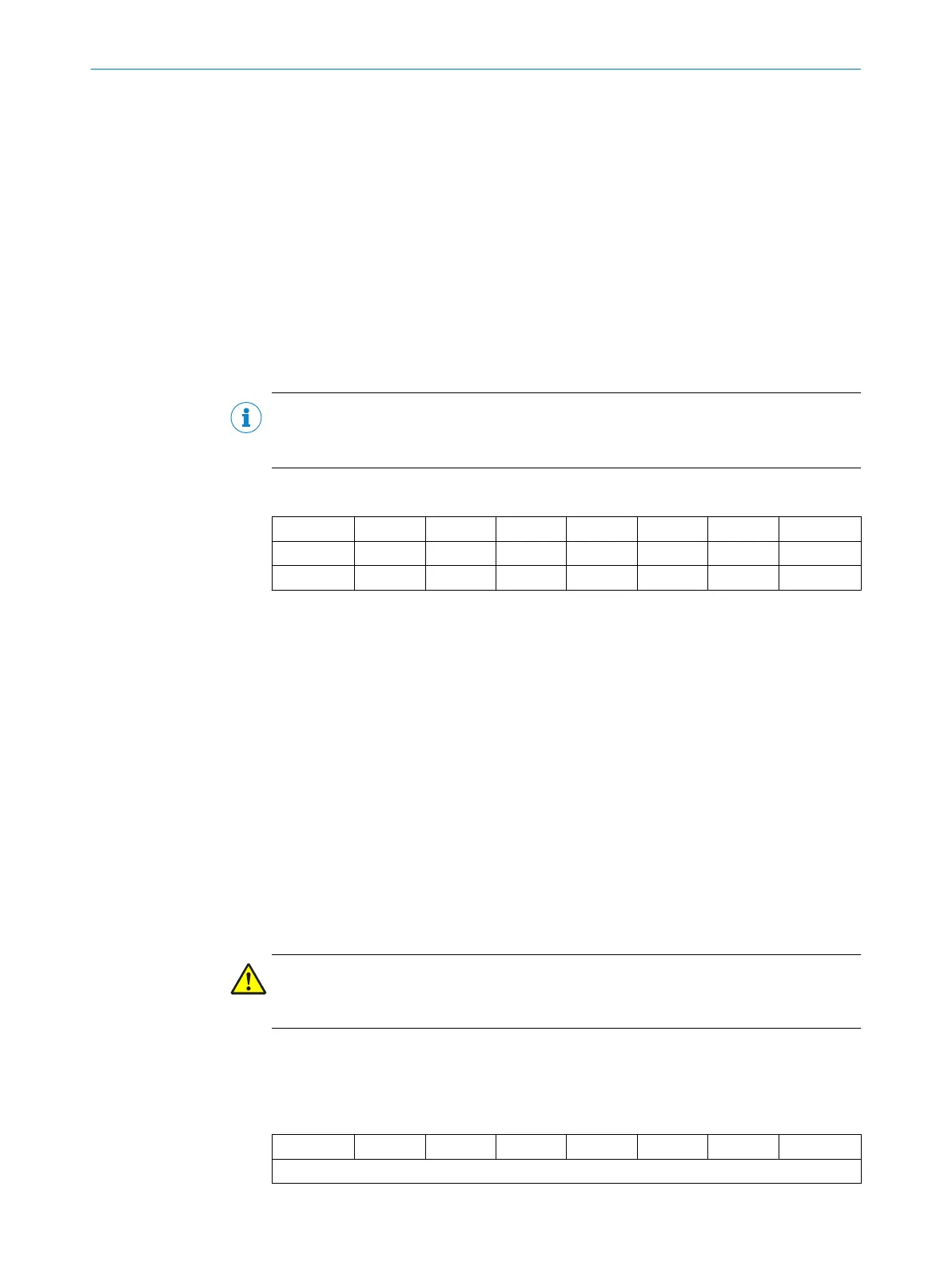

Register 08h:

Summary mask

W-0 W-0 W-0 W-0 W-0 W-0 W-0 W-0

MSUM7 MSUM6 MSUM5 MSUM4 MSUM3 MSUM2 MSUM1 MSUM0

Bit 7 Bit 0

Bit 7-0 MSUM7:MSUM0: Mask for status summary bits

1 = In the set status, the corresponding status summary bit sets the SUM event moni‐

toring and the signal at the interrupt pin.

0 = In the set status, the corresponding status summary bit does not set the SUM event

monitoring and the signal at the interrupt pin.

6.3.7 Edges

The EDGES edge register contains the time control for the DSL cable bit sampling and

can be used to monitor the connection quality.

Each individual edge register bit is set if, at system start-up, an edge of the test signal is

detected during the time period of the corresponding bit. An edge is defined as a

change in cable value between successive detections. The sampling is carried out eight

times as fast as the cable bit rate.

Clean cable signals mean that only a few bits are set in the edge register, whilst noisy

cable signals set a large number of bits.

CAUTION

If all bits in the edge register are set, this is an indication of excessive interference in

the cable in which no connection can be established.

The register is write protected. The content of this register does not change after the

start-up phase. A new bit sampling pattern is only generated after a forced reset of the

protocol.

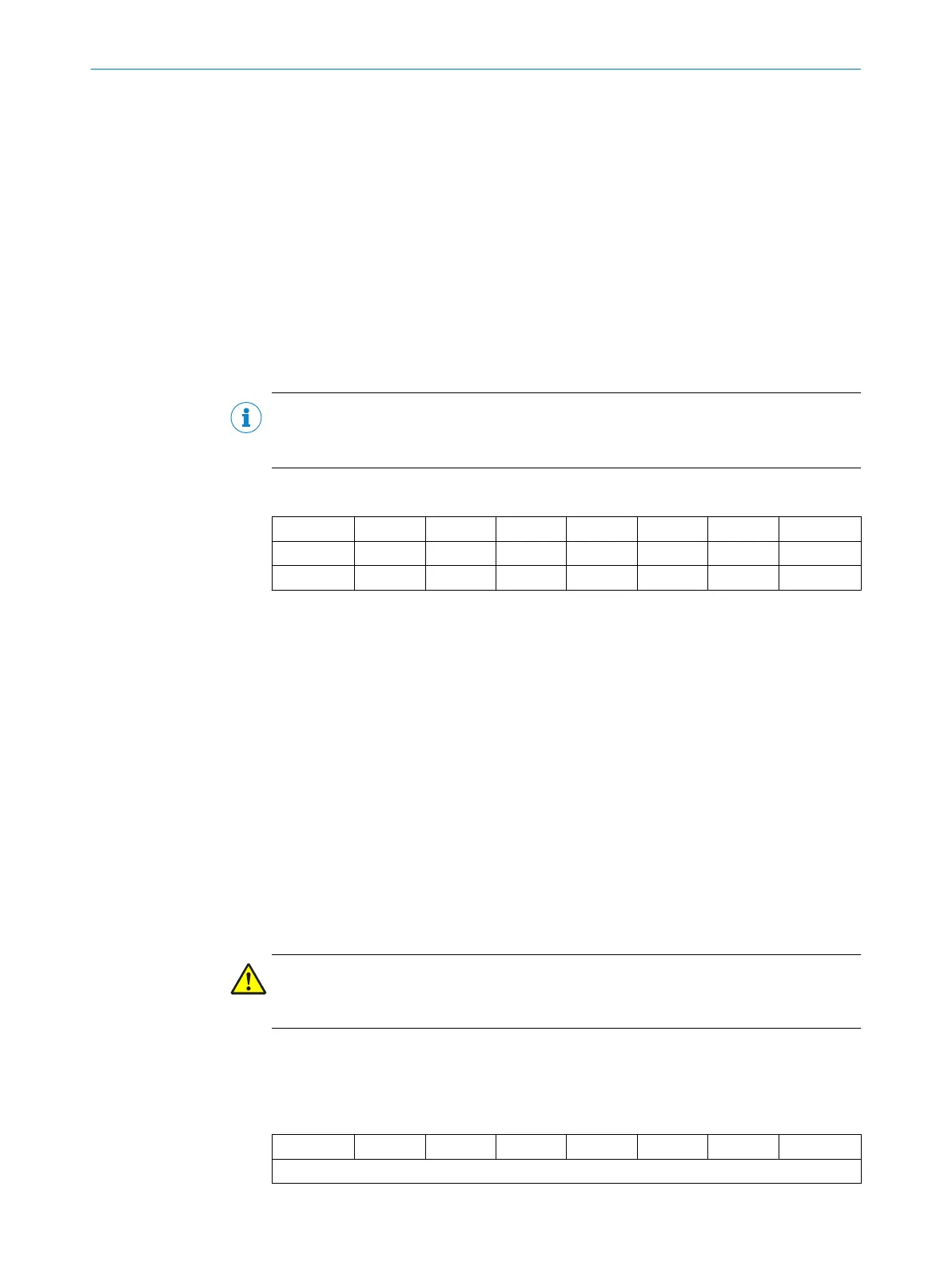

Register 09h: Edges

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

Bit sampling pattern

REGISTER MAP 6

8017595/ZTW6/2018-01-15 | SICK T E C H N I C A L I N F O R M A T I O N | HIPERFACE DSL

®

41

Subject to change without notice

Loading...

Loading...