• FTDI FT4232 USB-to-JTAG/USB-UART device (U20) connected to USB 3.1 type-C connector

(J207)

• JTAG pod at cable connector J36 (2 mm 2x7 shrouded/keyed)

See the "FT4232HL UART Interface Connecons" gure in PMC MIO[42:43] UART0 for an

overview of FT4232 U20 JTAG and USB-UART connecvity.

Clock Generation

The VCK190 board provides xed and variable clock sources for the XCVC1902 U1 ACAP and

other funcon blocks. The following table lists the source devices for each clock.

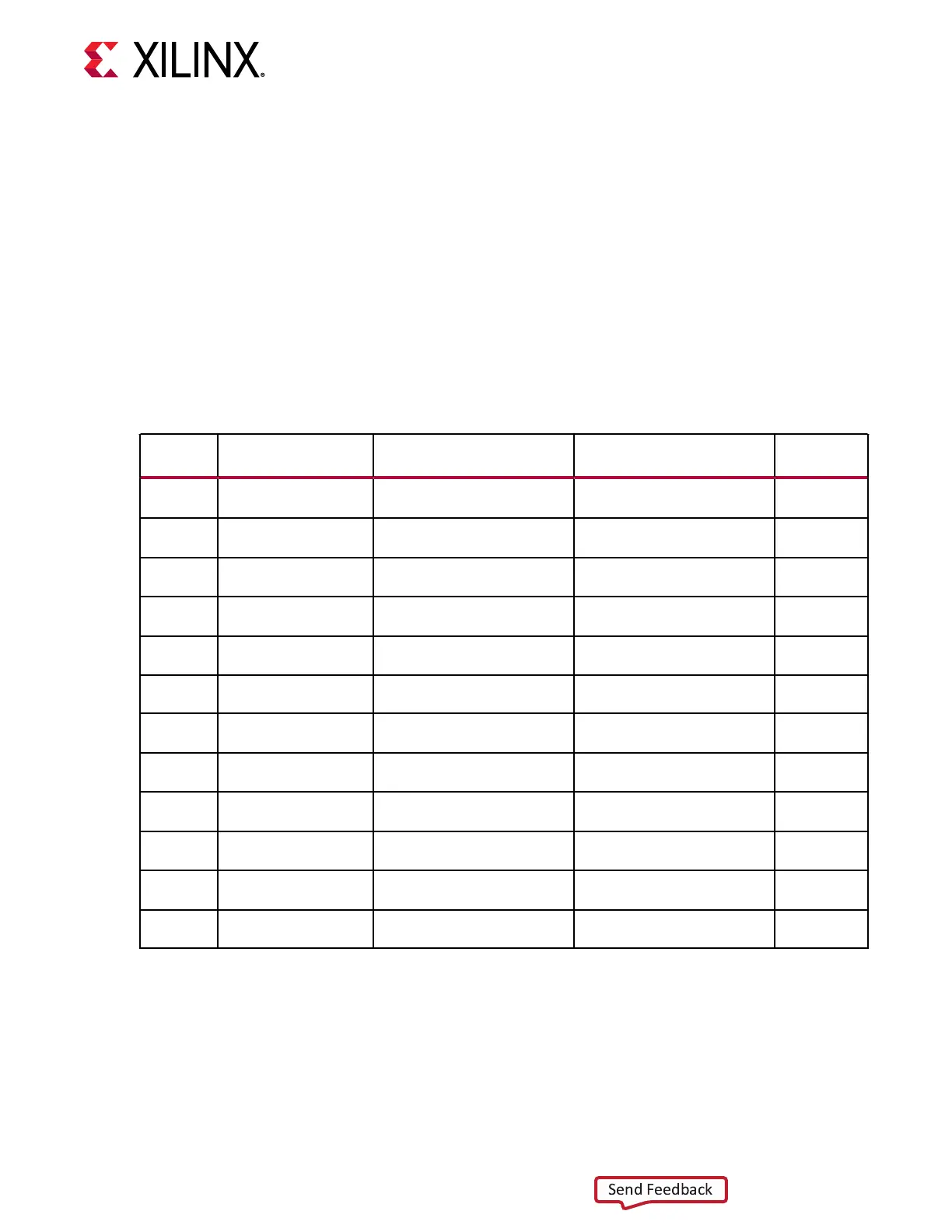

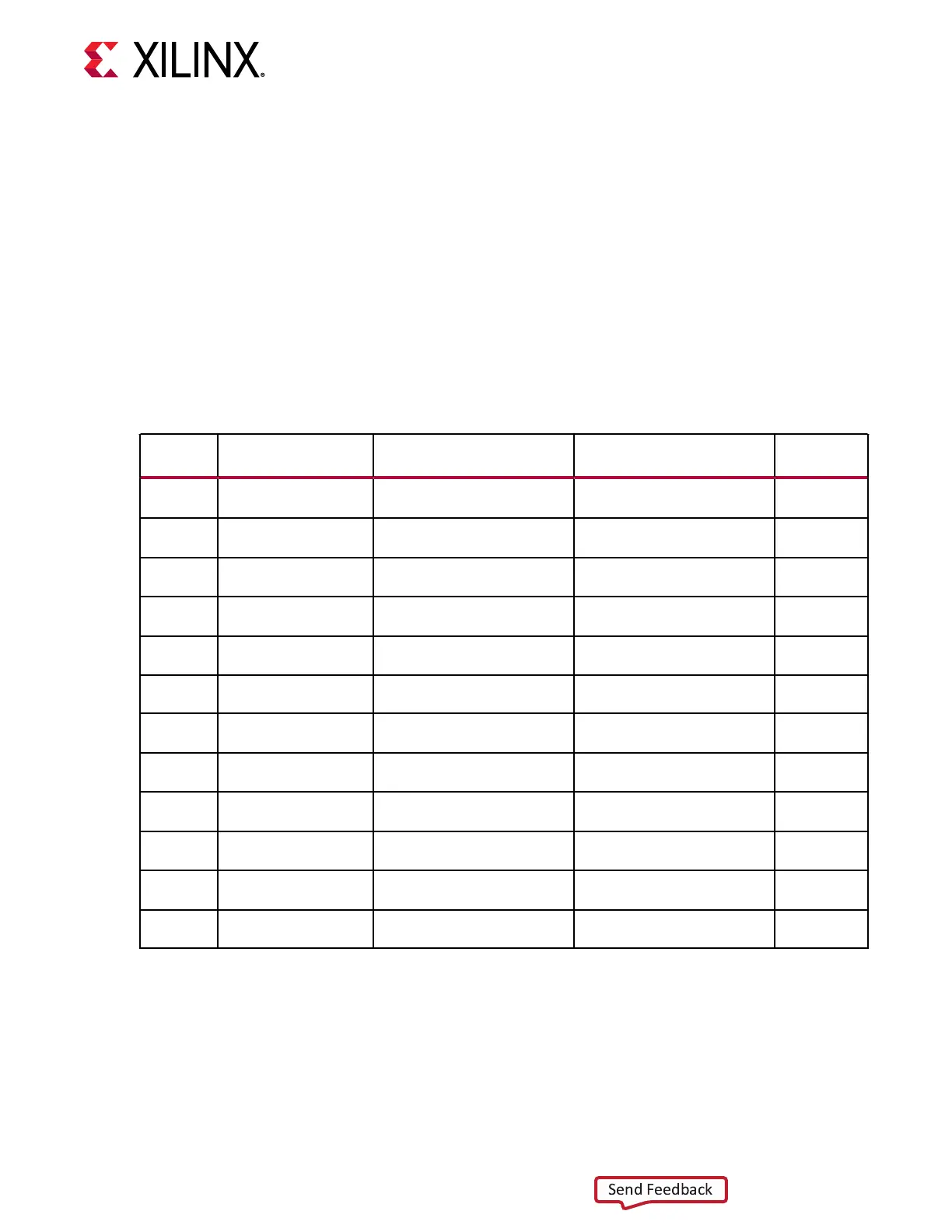

Table 17: Clock Sources

Callout Ref. Des. Feature Notes

Schematic

Page

36 U2 DDR4 DIMM CLK, 200 MHz, 3.3V

LVDS, 0x60

Silicon Labs SI570BAB000299DG 4

37 U3 LPDDR4 CLK2, 200 MHz, 3.3V

LVDS, 0x60

Silicon Labs SI570BAB000299DG 5

38 U4 LPDDR4 CLK1, 200 MHz, 3.3V

LVDS, 0x60

Silicon Labs SI570BAB000299DG 7

39 U5 HSDP CLK, 156.25 MHz, 3.3V

LVDS, 0x5D

Silicon Labs SI570BAB000544DG 8

40 U32 ACAP U1 REF CLK, 33.33 MHz,

1.8V CMOS, 0x5D

Silicon Labs SI570JAC000900DG 43

41 U39 PCIe jitter atten., 100 MHz, 3.3V

LVDS

IDT 85411AMLF 49

42 U62 HDMI jitter atten., 148.50 MHz,

3.3V LVDS, 0x6C

IDT 8T49N241-994NLGI 52

43 U142 SYSCTLR clocks 33.33 MHz & 125

MHz I2C 0x6A

Silicon Labs Si5332FD10259-

GM1

101

44 U192 zSFP CLK, 156.25 MHz, 3.3V

LVDS, 0x5D

Silicon Labs SI570BAB000544DG 8

45 U205 FMCP MGT CLK, 100 MHz, 3.3V

LVDS, 0x5F

Silicon Labs SI570BAC002038DG 48

46 U219 IEEE-1588 eCPRI CLK, various,

3.3V, 0x58

IDT 8A34001E-000AJG8 104

47 J328-J331 IEEE-1588 eCPRI 8A34001 CLK in

and out SMA pairs

Rosenberger 32K10K-400L5 104

The connecon details for ACAP U1 connected clocks described in this secon are documented

in the VCK190 board XDC le, referenced in Appendix B: Xilinx Design Constraints.

Programmable DDR4 DIMM SI570 Clock

[Figure 3, callout 36]

Chapter 3: Board Component Descriptions

UG1366 (v1.0) January 7, 2021 www.xilinx.com

VCK190 Board User Guide 45

Loading...

Loading...