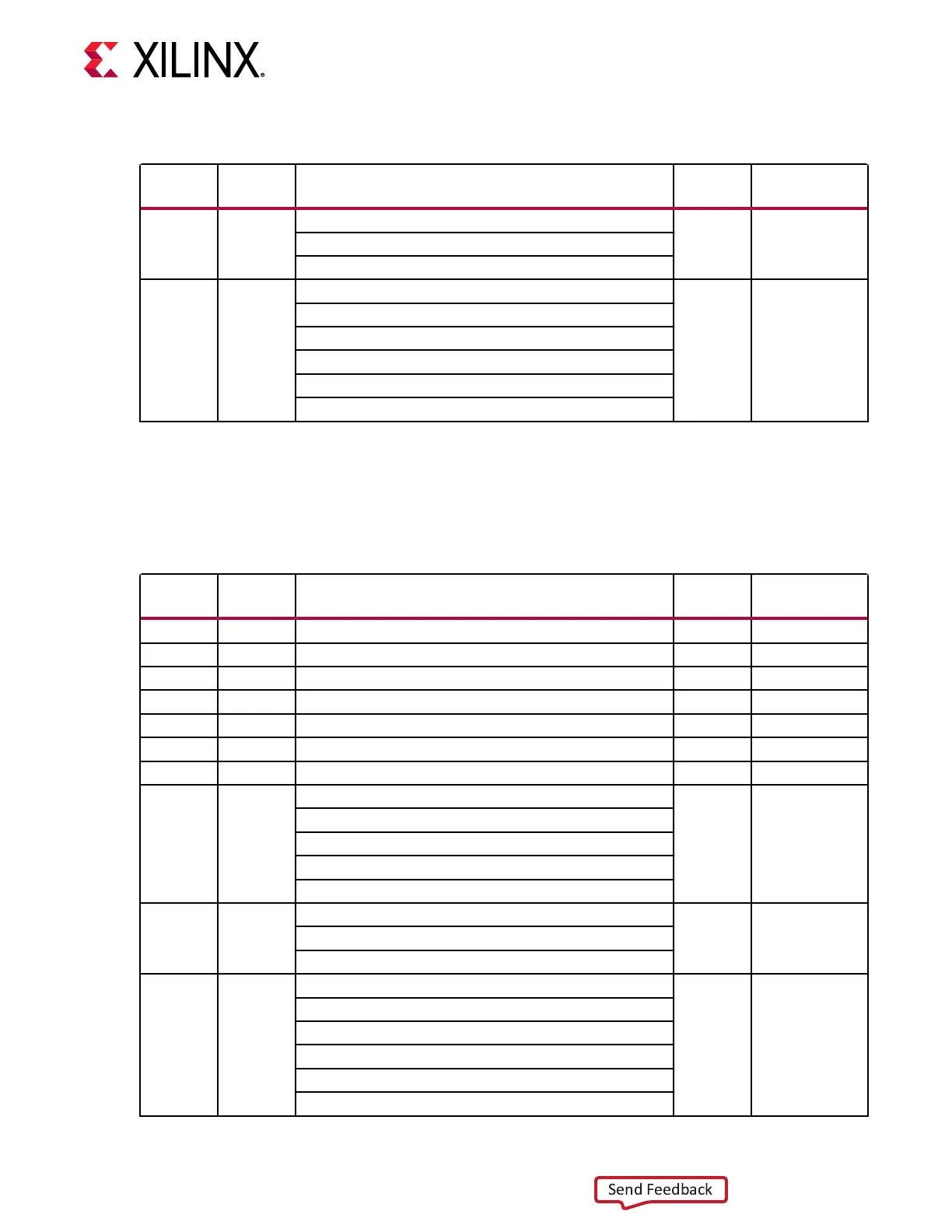

Table 3: Default Jumper Settings (cont'd)

Callout

Number

Ref. Des. Function Default

Schematic

Page

11 J306

Si53340 clock MUX U206 input select

OFF 48

ON: CLK1 8a34001_Q2

OFF: U205 USER_SI570_1(100 MHz default)

12 J326

POR_B source select (OR’d with POR_B)

1-2

3-4

7-8

15

None: U10 TPS389001 POR only

1-2: U125 SYSCTLR_POR_B

3-4: J36 PC4_POR_B

5-6: J212(B) DC_PS_POR_B_OUT

7-8: U20 FTDI_POR_B

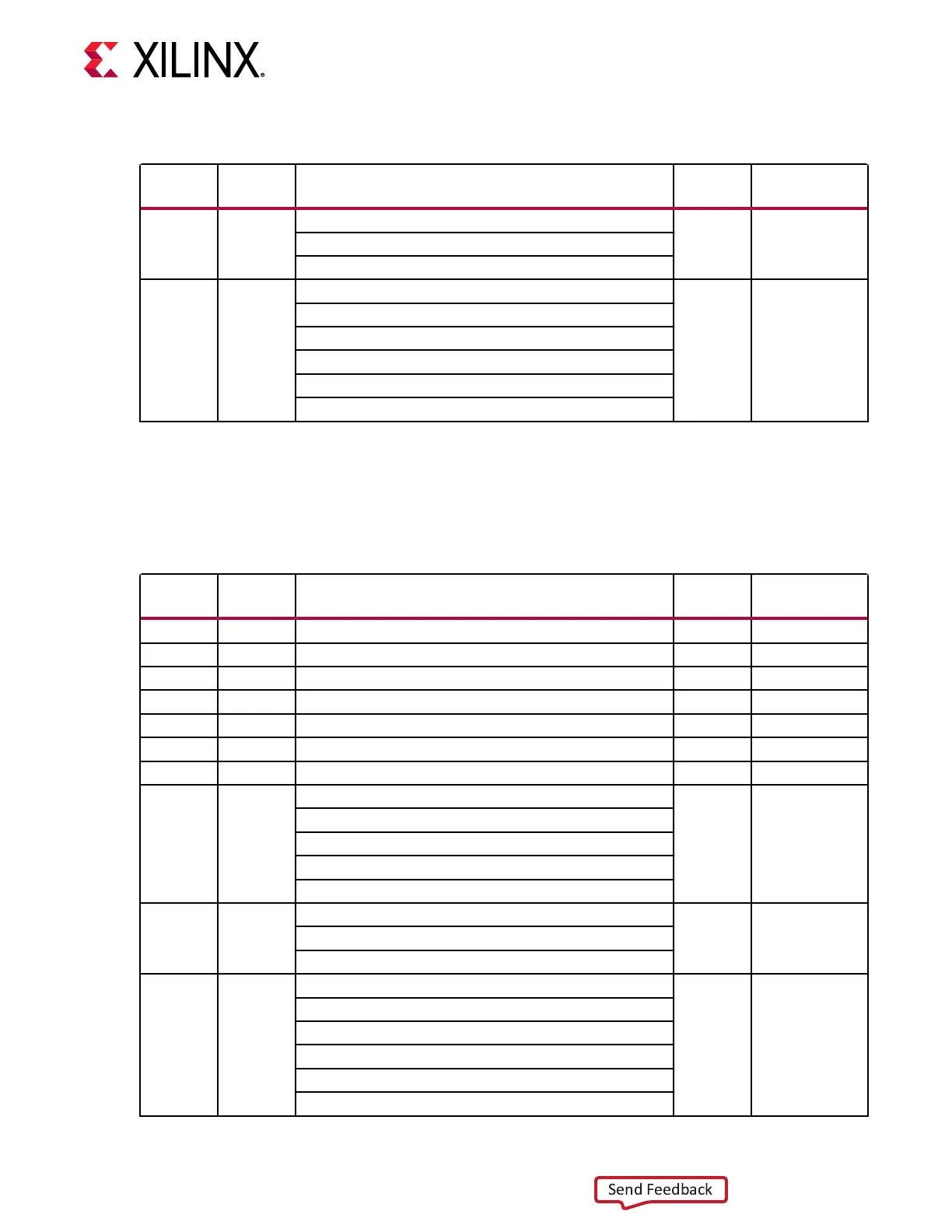

Switches

The following table lists the default switch sengs.

Table 4: Default Switch Settings

Callout

Number

Ref. Des. Function Default

Schematic

Page

13 SW1 ACAP U1 mode 4-pole DIP switch 0000 14

Switch OFF = 1 = High; ON = 0 = Low

Mode = SW1[4:1] = Mode[3:0]

JTAG = ON,ON,ON,ON = 0000

QSPI32 = ON,ON,OFF,ON = 0010

SD = OFF,OFF,OFF,ON = 1110

Reserved for Xilinx

®

= OFF,OFF,OFF,OFF = 1111

14 SW3

JTAG MUX select 2-pole DIP switch

01 24

Switch OFF = 1 = High; ON = 0 = Low

SW3[1:2] = MUX[S0:S1]

SYSCTLR U125 BANK 44 = ON,ON = 00

FTDI BRIDGE U20 = ON,OFF = 01

15 SW6

ACAP U1 BANK 306 GPIO 4-Pole DIP switch

0000 53

SW6[4:1] = GPIO_DIP_SW[0:3]

Switch OFF = 0 = Low; ON = 1 = High

16 SW11

ZU4 SYSCTLR U125 Mode 4-Pole DIP switch

0000 89

Switch OFF = 1 = High; ON = 0 = Low

Mode = SW11[4:1] = Mode[3:0]

JTAG = ON,ON,ON,ON = 0000

QSPI32 = ON,ON,OFF,ON = 0010

SD = OFF,OFF,OFF,ON = 1110

Chapter 2: Board Setup and Configuration

UG1366 (v1.0) January 7, 2021 www.xilinx.com

VCK190 Board User Guide 20

Loading...

Loading...