Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com 23

UG074 (v2.2) February 22, 2010

Ethernet MAC Signal Descriptions

R

Client-Side Receive (RX) Signals

Table 2-2 describes the client-side receive signals. These signals are used by the Ethernet

MAC to transfer data to the client.

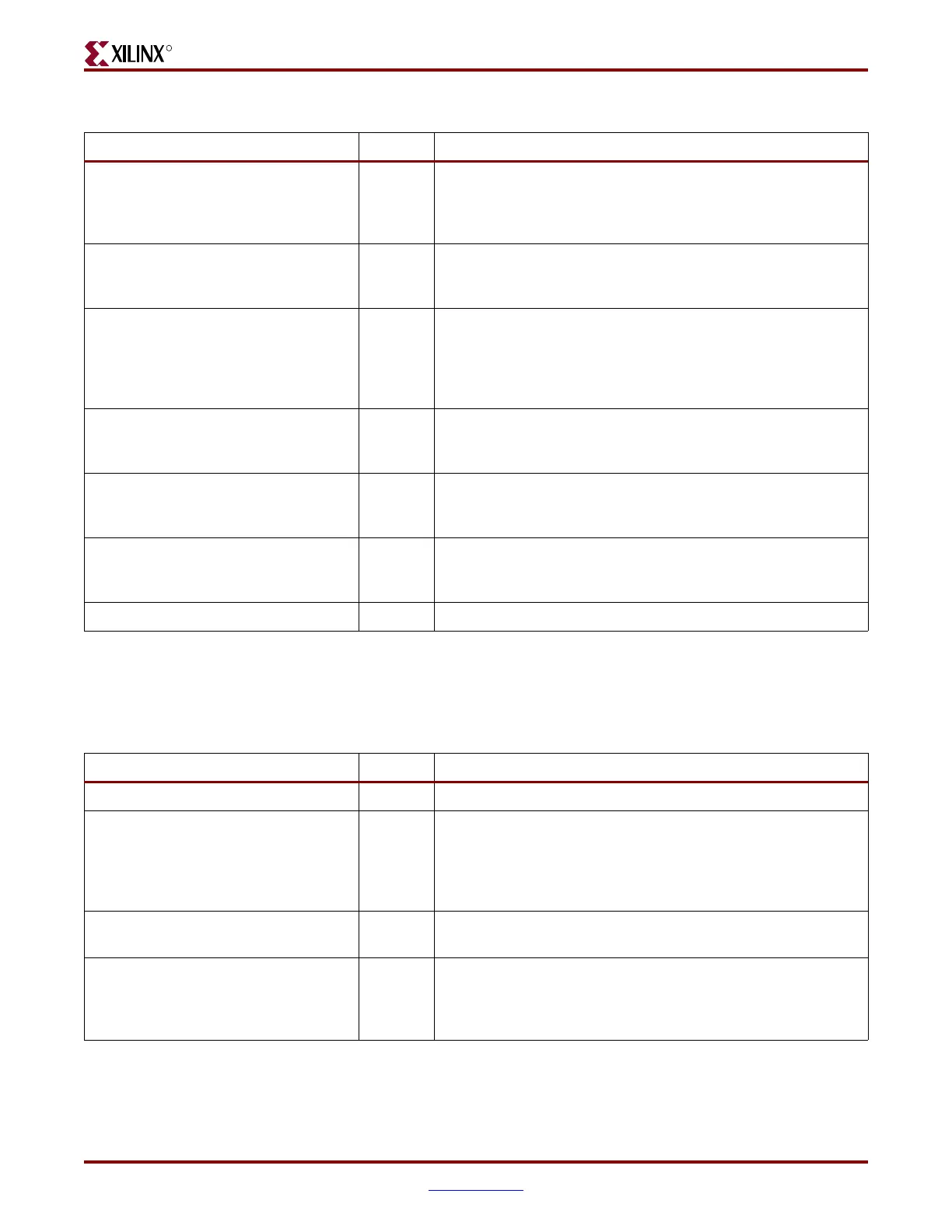

EMAC#CLIENTTXACK Output

Handshake signal – Asserted when the Ethernet MAC accepts

the first byte of data. On the next and subsequent rising clock

edges, the client must provide the remainder of the frame data.

See “Normal Frame Transmission” in Chapter 3.

EMAC#CLIENTTXCOLLISION Output

Asserted by the Ethernet MAC to signal a collision on the

medium. Any transmission in progress should be aborted. This

signal is always deasserted in full-duplex mode.

EMAC#CLIENTTXRETRANSMIT Output

Asserted by the Ethernet MAC at the same time as the

EMAC#CLIENTTXCOLLISION signal. The client should re-

supply the aborted frame to the Ethernet MAC for

retransmission. This signal is always deasserted in full-duplex

mode.

EMAC#CLIENTTXSTATS Output

The statistics data on the last data frame sent. The 32-bit TX raw

statistics vector is output by one bit per cycle for statistics

gathering. See “Transmitter Statistics Vector” in Chapter 3.

EMAC#CLIENTTXSTATSBYTEVLD Output

Asserted if an Ethernet MAC frame byte is transmitted

(including destination address to FCS). This is valid on every TX

clock cycle.

EMAC#CLIENTTXSTATSVLD Output

Asserted by the Ethernet MAC after a frame transmission to

indicate a valid EMAC#CLIENTTXSTATS output. See

“Transmitter Statistics Vector” in Chapter 3.

EMAC#CLIENTTXCLIENTCLKOUT Output See “Transmit Clocking Scheme” in Chapter 5.

Table 2-1: Transmit Client Interface Signals (Cont’d)

Signal Direction Description

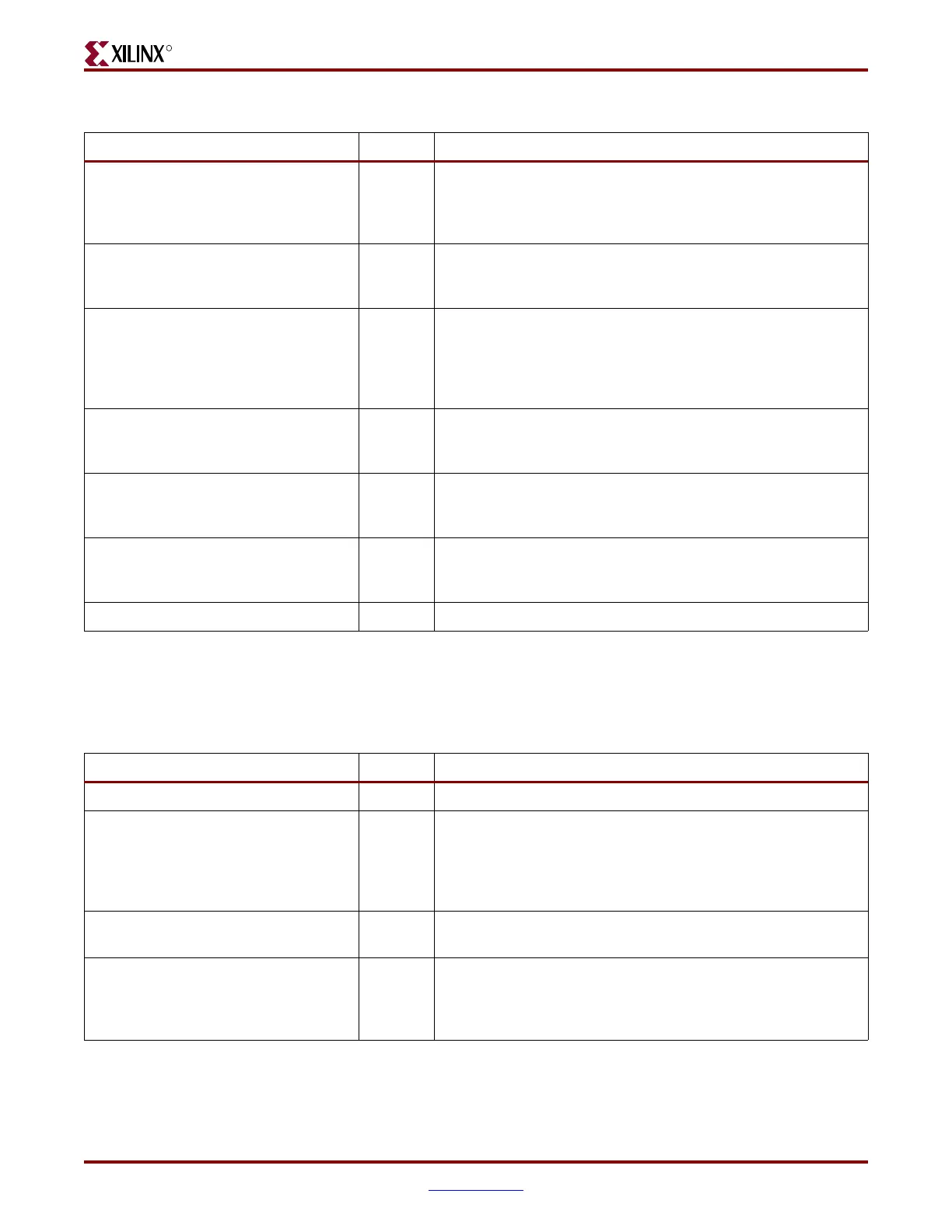

Table 2-2: Receive Client Interface Signals

Signal Direction Description

CLIENTEMAC#RXCLIENTCLKIN Input See “Receive Clocking Scheme” in Chapter 5.

EMAC#CLIENTRXD[15:0] Output

Frame data received from the Ethernet MAC. The data path can

be configured to either 8 bits or 16 bits wide. Bits [7:0] are used for

8-bit width. The 16-bit interface is intended to be used in

1000BASE-X PCS/PMA mode. See “Receive (RX) Client – 16-bit

Wide Interface” in Chapter 3.

EMAC#CLIENTRXDVLD Output

The Ethernet MAC indicates to the client the receipt of valid

frame data.

EMAC#CLIENTRXFRAMEDROP Output

This signal is asserted to notify the client that an incoming receive

frames destination address does not match any addresses in the

address filter. The signal functions even when the address filter is

not enabled.

Loading...

Loading...