32 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

UG074 (v2.2) February 22, 2010

Chapter 2: Ethernet MAC Architecture

R

Unicast Address

Table 2-12 describes the 48 tie-off pins (TIEEMAC#UNICASTADDR[47:0]) used to set the

Ethernet MAC address for the Virtex-4 FPGA Embedded Tri-Mode Ethernet MAC.

Management Data Input/Output (MDIO) Interface Signals

Table 2-13 describes the Management Data Input/Output (MDIO) interface signals. The

MDIO format is defined in IEEE Std 802.3, Clause 22.

Mode-Dependent Signals

The Ethernet MAC has several signals that change definition depending on the selected

operating mode. This section describes the basic signals in the various operating modes.

Data and Control Signals

Table 2-14 shows the data and control signals for the different modes. They are set from the

tie-off pins. These signals are multiplexed, and their functionality is defined when the

mode is set.

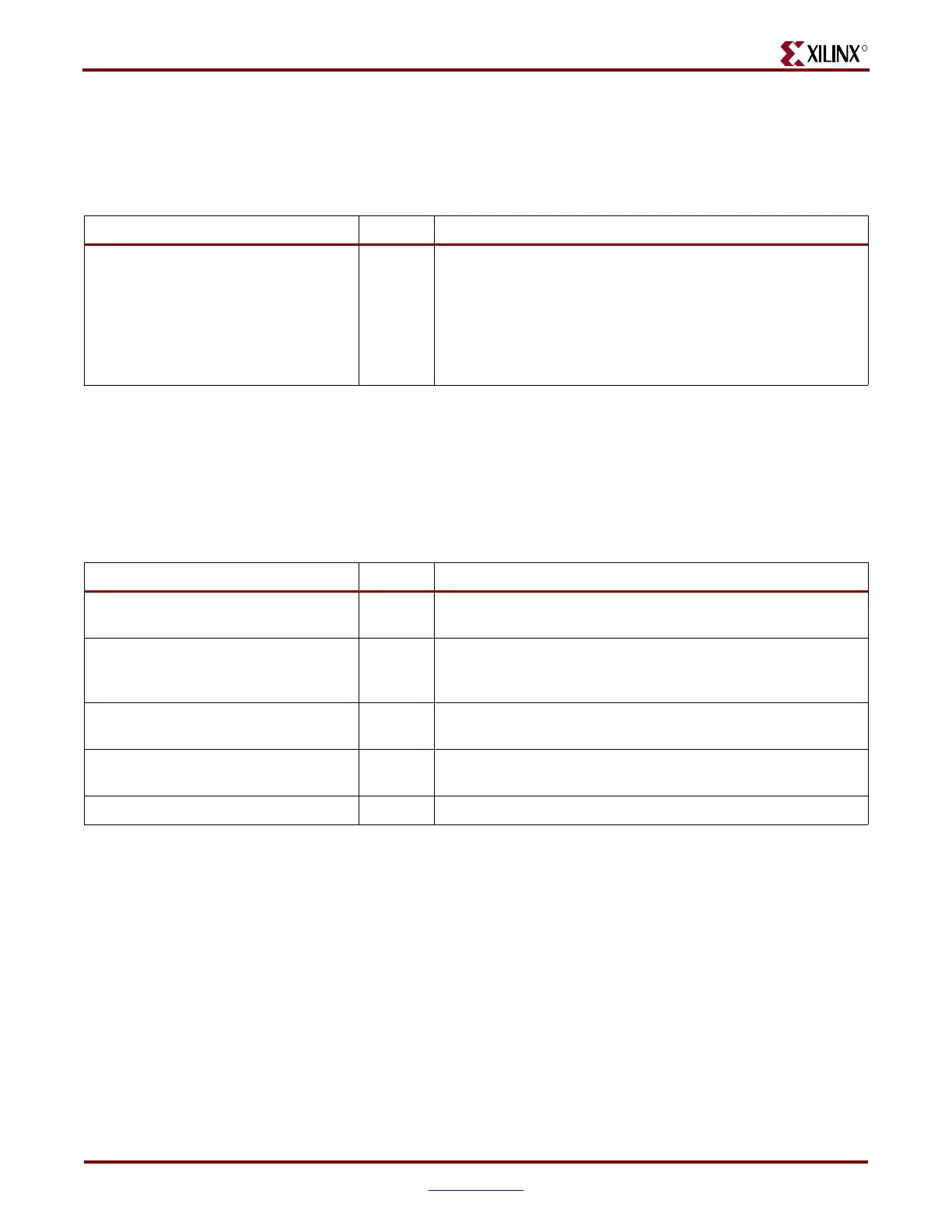

Table 2-12: Unicast Address Pins

Signal Direction Description

TIEEMAC#UNICASTADDR[47:0] Input

This 48-bit wide tie-off is used to set the Ethernet MAC unicast

address used by the address filter block to see if the incoming

frame is destined for the Ethernet MAC.

The address is ordered for the least significant byte in the register

to have the first byte transmitted or received; for example, an

Ethernet MAC address of 06-05-04-03-02-01 is stored in byte

[47:0] as 0x010203040506.

Notes:

1. All of the TIEEMAC#UNICASTADDR[47:0] bits are registered on input and can be treated as asynchronous inputs.

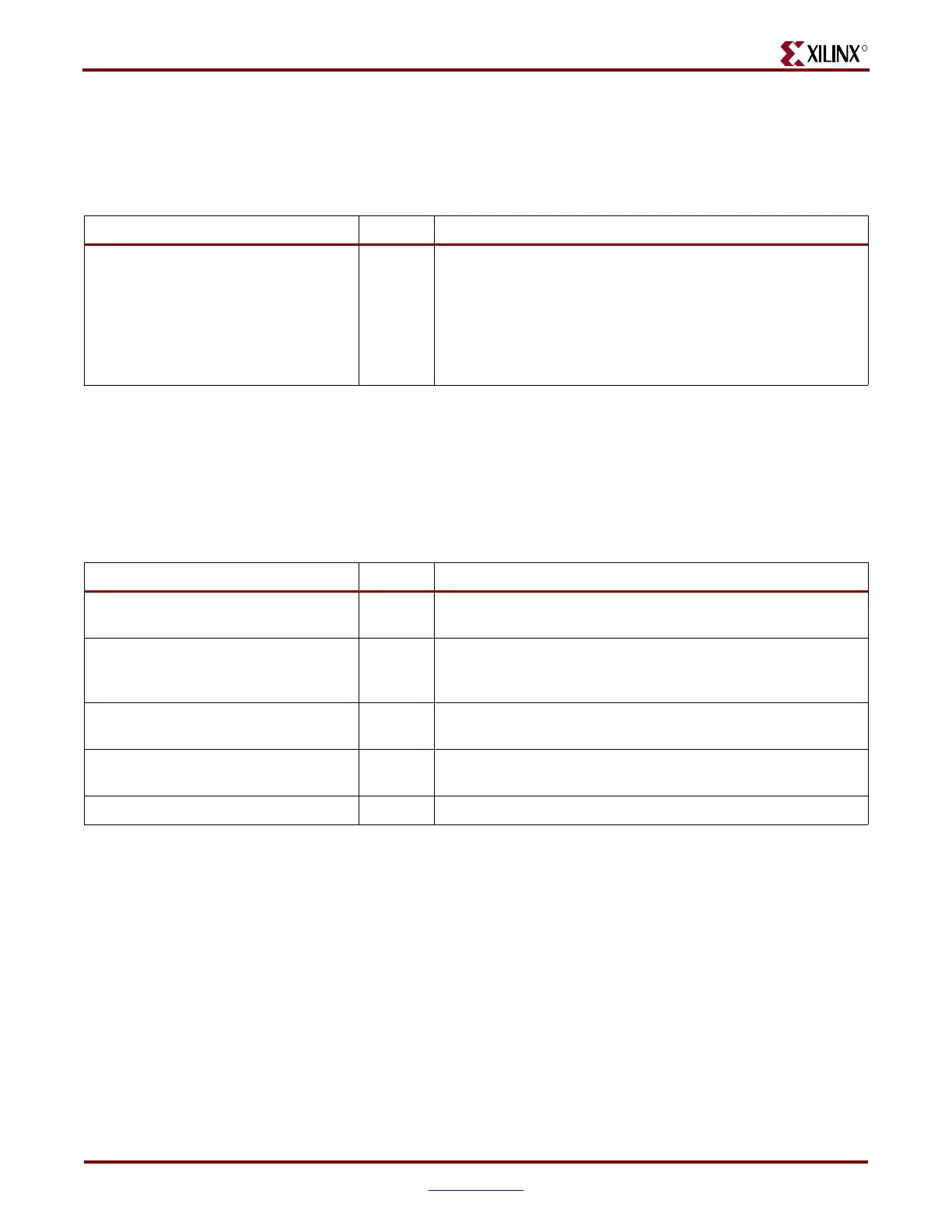

Table 2-13: MDIO Interface Signals

Signal Direction Description

EMAC#PHYMCLKOUT Output

Management clock derived from the host clock or

PHYEMAC#MCLKIN.

PHYEMAC#MCLKIN Input

When the host is not used, access to the PCS must be provided by

an external MDIO controller. In this situation, the management

clock is an input to the core.

PHYEMAC#MDIN Input

Signal from the physical interface for communicating the

configuration and status. If unused, must be tied High.

EMAC#PHYMDOUT Output

Signal to output the configuration and command to the physical

interface.

EMAC#PHYMDTRI Output The 3-state control to accompany EMAC#PHYMDOUT.

Loading...

Loading...