ZC702 Board User Guide www.xilinx.com 50

UG850 (v1.7) March 27, 2019

Feature Descriptions

PMOD connectors J62 and J63 are wired to the U1 XC7Z020 SoC via TXS0108E 3.3V-to-VADJ

(typically 1.8V) level-shifters.

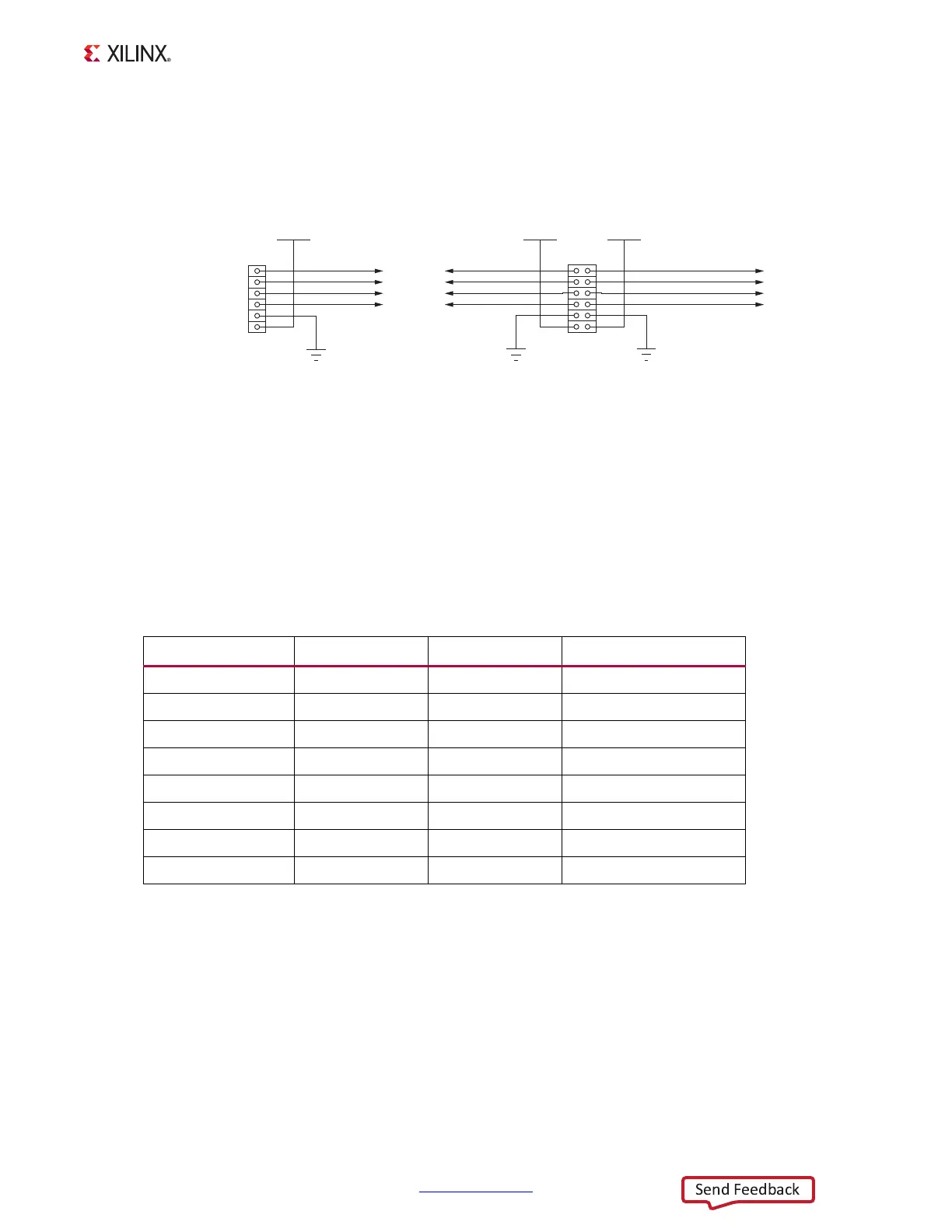

Figure 1-25 shows the user GPIO male pin header circuits.

When using the PMOD headers on the Zynq-7000 SoC ZC702 evaluation kit, the voltage

level output might appear normal at steady state; however, the rise and fall times on the

other side of the TXS0108E level shifters can be several microseconds. The paralleled LED

driver NDS331N FET has a gate capacitance of ~200 pF. The 200 pF load affects maximum

toggle rate, which is ~100 kHz. There are no speed requirements for PMOD or GPIOs. The

recommendation for a specific high-speed access with GPIO is to use the FMC interface.

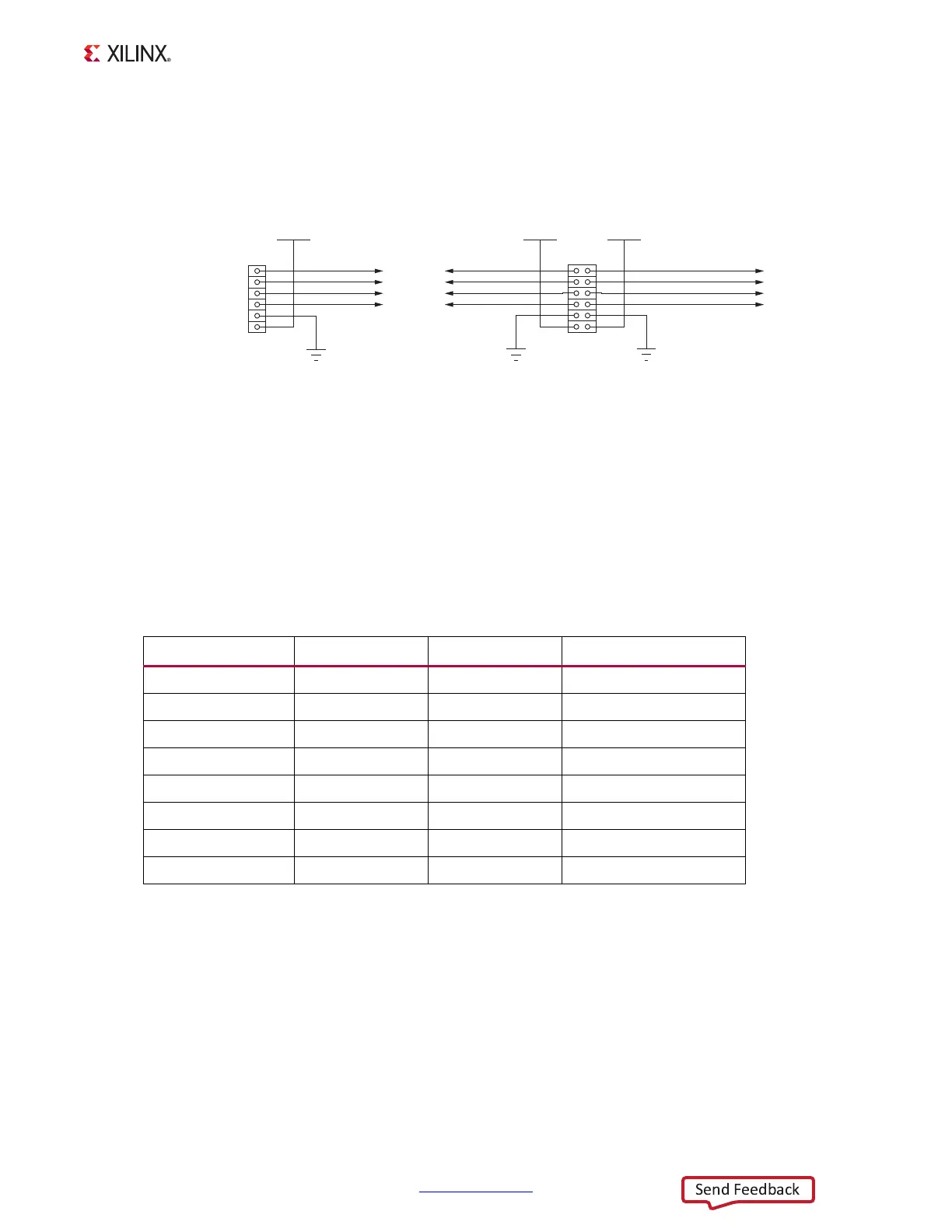

Table 1-27 lists the GPIO Header connections to XC7Z020 SoC U1.

Refer to the Zynq-7000 SoC Technical Reference Manual

(UG585) [Ref 2] for information

about the PS PJTAG functionality.

X-Ref Target - Figure 1-25

Figure 1-25: User GPIO Headers

Table 1-27: GPIO Header Connections to XC7Z020 SoC at U1

XC7Z020 (U1) Pin Net Name I/O Standard GPIO Header and Pin

E15 PMOD1_0 LVCMOS25 J63.1

D15 PMOD1_1 LVCMOS25 J63.3

W17 PMOD1_2 LVCMOS25 J63.5

W5 PMOD1_3 LVCMOS25 J63.7

V7 PMOD2_0 LVCMOS25 J62.1

W10 PMOD2_1 LVCMOS25 J62.2

P18 PMOD2_2 LVCMOS25 J62.3

P17 PMOD2_3 LVCMOS25 J62.4

UG850_c1_25_030513

PL PJTAG TDI LS

PMOD1 0

J63

1

3

5

7

9

11

2

4

6

8

10

12

GND

VCC3V3

VCC3V3

GND

J62

1

2

3

4

5

6

PMOD2 0

PMOD2 1

PMOD2 2

PMOD2 3

GND

VCC3V3

PL PJTAG TMS LS

PL PJTAG TCK LS

PL PJTAG TDO LS

PMOD1 1

PMOD1 2

PMOD1 3

Loading...

Loading...